# CMPUT 329 - Computer Organization and Architecture II Quiz # 5 — Fall 2003

Prof. José Nelson Amaral Computing Science Department University of Alberta

## Name: SOLUTION

### CMPUT 329 Honor Code

By turning in the quiz solution for grading, I certify that I have worked all the solutions on my own, that I have not copied or transcribed solutions from a classmate, someone outside the class, or from any other source. I also certify that I have not facilitated or allowed any of my classmates to copy my own solutions. I am aware that the violation of this honor code constitutes a breach of the trust granted me by the teaching staff, compromises my reputation, and subjects me to the penalties prescribed in Section 26.1 of the University of Alberta 2003/2004 Calendar.

Edmonton, November, 2003.

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

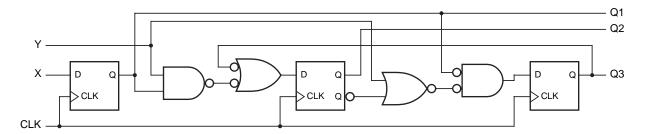

| Figure 1. A sequential circuit using D Filp-hops. |            |           |           |           |  |  |  |  |

|---------------------------------------------------|------------|-----------|-----------|-----------|--|--|--|--|

| Current State                                     | Next State |           |           |           |  |  |  |  |

| Q1 Q2 Q3                                          | X=0 & Y=0  | X=0 & Y=1 | X=1 & Y=0 | X=1 & Y=1 |  |  |  |  |

| 000                                               | 011        | 011       | 111       | 111       |  |  |  |  |

| 001                                               | 001        | 001       | 101       | 101       |  |  |  |  |

| 010                                               | 010        | 011       | 110       | 111       |  |  |  |  |

| 011                                               | 000        | 001       | 100       | 101       |  |  |  |  |

| 100                                               | 010        | 010       | 110       | 110       |  |  |  |  |

| 101                                               | 000        | 010       | 100       | 110       |  |  |  |  |

| 110                                               | 010        | 010       | 110       | 110       |  |  |  |  |

| 111                                               | 000        | 010       | 100       | 110       |  |  |  |  |

Figure 1: A sequential circuit using D Flip-flops.

Table 1: State Transition Table for the sequential circuit of Figure 1.

#### Question 1 (50 points):

In this question you will analyse the sequential circuit shown in Figure 1.

a. (25 points) Write the excitation equations and the output equations for the circuit.

D1 = X D2 = Q1.Y + Q3' D3 = Q1'.(Q2' + Y) = Q1'.Q2' + Q1'.Y

#### b. (25 points) Complete the State Transition Table 1.

It is easier to read the columns in the table.

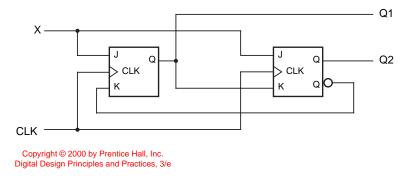

Figure 2: A sequential circuit using JK Flip-flops.

#### Question 2 (30 points):

For this question, it might be useful to recall the Application table for J-K flip-flops that is presented on page 577 of your textbook:

| Q | $\mathbf{Q}+$ | J | Κ |

|---|---------------|---|---|

| 0 | 0             | 0 | Х |

| 0 | 1             | 1 | Х |

| 1 | 0             | Х | 1 |

| 1 | 1             | Х | 0 |

This table provides the values that you have to have in the inputs J and K of the J-K flip-flop when you want to effect a transition from the current state Q to the next state Q+. An X in the table indicates a don't care.

You will analyse the sequential circuit built with two J-K flip-flops shown in Figure 2. Assume that the four states in this machine are A, B, C, and D, and the following state assignment: (A:00), (B:01), (C:10), and (D:11). Assume also that 01 indicates that Q1=0 and Q2=1.

a. (25 points) Complete the following state transition table.

| Current State | Next State |     | Outputs |    |

|---------------|------------|-----|---------|----|

| Q1 Q2         | X=0        | X=1 | Q1      | Q2 |

| 00            | 00         | 11  | 0       | 0  |

| 01            | 01         | 11  | 0       | 1  |

| 10            | 00         | 01  | 1       | 0  |

| 11            | 10         | 10  | 1       | 1  |

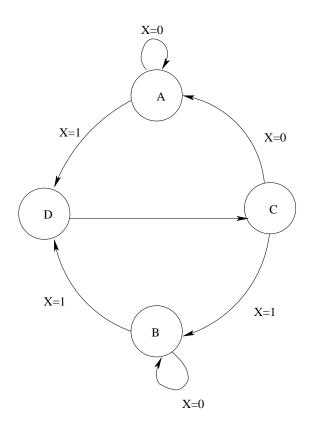

Figure 3: State Diagram for FSM implemented by circuit of Figure 2.

b. (25 points) Complete the drawing of the state diagram of Figure 3 for the finite state machine implemented by the circuit of Figure 2.