Copyright

by

José Nelson Amaral

1994

## A PARALLEL ARCHITECTURE FOR SERIALIZABLE PRODUCTION SYSTEMS

by

### JOSÉ NELSON AMARAL, B.E., M.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN December 1994

# A PARALLEL ARCHITECTURE FOR SERIALIZABLE PRODUCTION SYSTEMS

APPROVED BY DISSERTATION COMMITTEE:

Supervisor: \_\_\_\_\_

## Acknowledgments

I am deeply thankful to my advisor, Prof. Joydeep Ghosh, for many enlighting discussions, for coherent and sound advising, for his patience in carefully reviewing all my writings, and for his great availability. Prof. Ghosh and I developed an excellent working relationship in which I felt free to pursue my own research interests. At the same time I could count with his help and guidance whenever I felt I could not continue on my own. When I depart from Austin, I bring with me not only the academic knowledge but also an inspiring example to base the construction of good relationships with my own students.

I appreciated the fruitful discussions with Prof. Daniel Miranker, Prof. Sanqi Li, Prof. Ben Kuipers, and Prof. Vijaya Ramachandran when I needed help in conducting my research.

It would have greatly extended my stay in graduate school have I had to write the simulator from scratch. I am very thankful to Anurag Acharya of Carnegie Mellon University who graciously let me use the front-end of his own simulator. Anurag was also very helpful with many questions and provided some of the benchmarks used to test the architecture. I would also like to acknowledge Howard Owens of Microelectronics and Computer Technology Corporation (MCC) for tracking a difficult bug in the implementation of the simulator.

I was very fortunate to meet many helpful people in my passage through graduate school. Among the staff: Mellanie Gulick, Adela Baines, and Shiree Schade. My officemates that were willing to proofread pieces of my work, or to listen when I felt the need to verbalize explanations to problems in my research: Jeff Draper, Kagan Tumer, and our "adopted officemate" Guillaume Brat. A big thanks to our volunteer system administrators: Alex Tomlinson, Jeff Draper, Thomas Callaway, and specially Kurt Bollacker for the numerous hours they spent to make sure that our systems were functional.

The financial support for my graduate studies came from Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq), a Brazilian government agency for the development of science and technology and from Pontifícia Universidade Católica do Rio Grande do Sul (PUCRS). At PUCRS I am specially thankful to Profs. Urbano Zilles, Dulcemar Coelho Lautert, Juarez Seagebin Correa, and Hernan Crosa Berni who always demonstrated great support for the continuation of my education.

And last, but definitely not least, a very big thanks to all my friends that made my living in Austin so interesting. I sure will miss y'all.

José Nelson Amaral

The University of Texas at Austin December 1994

#### A PARALLEL ARCHITECTURE FOR SERIALIZABLE PRODUCTION SYSTEMS

Publication No.

José Nelson Amaral, Ph.D. The University of Texas at Austin, 1994

Supervisor: Joydeep Ghosh

This dissertation introduces a new parallel architecture for implementing production systems. Key innovations include the elimination of global synchronization before each production firing and the overlapping between the matching and the select-act phases of Production Systems. These innovations are made possible by the use modern associative memory devices as control supporting structures. Allowing a production to fire before the matching of previous production firings is complete proved to be very efficient. The results produced by the architecture are proven to be correct according to the serializability criterion.

The development of a new benchmark addresses the lack of good benchmarks for the study of novel production system architectures. This benchmark allows for variations in the number of productions, database size, size of local data clusters, and ratio between local and global data.

A study of the production partition problem resulted in four different algorithms. These algorithms take into consideration processor workload balance, production interdependency, replication of data in memory, and reduction of communication traffic. Experimental studies with a comprehensive event driven simulator indicate that the use of dynamic information from previous runs produces more successful algorithms.

A comparative study with a parallel architecture that does global synchronization before every production firing shows that both improvements, namely the elimination of global synchronization and the overlapping between matching, selecting and firing, are very effective in improving the performance of production systems. Further measurements indicate that only a modest amount of associative memory is needed for this architecture and that the use of a bus as an interconnection network does not constitute a bottleneck.

Finally, a multiple functional unit Rete Network is considered within each processor of the architecture. New synchronization problems appear when multiple tokens are concurrently propagated through the Rete Network. Two synchronizing buffers assure correct operation of the architecture. Performance evaluations through system simulation and through analytical modeling indicate that using a modest number of functional units in the Rete Network is cost effective, but the architecture clearly yields diminishing returns when tens of functional units are used.

# **Table of Contents**

| Acknowledgments                              | iv           |  |

|----------------------------------------------|--------------|--|

| Abstract                                     | vi           |  |

| Table of Contents                            | viii         |  |

| List of Figures                              | xii          |  |

| List of Tables                               | XV           |  |

| List of Abbreviations and Acronyms           | xvii         |  |

| List of Symbols xix                          |              |  |

| Chapter 1. Introduction 1                    |              |  |

| Chapter 2. Background                        | 9            |  |

| 2.1 A Generic Production System Architecture | · · · · · 10 |  |

| 2.2 The Matching Engine                      | · · · · · 12 |  |

| 2.3 Current Research and Trends              | · · · · · 15 |  |

| 2.4 Read-Write Ratio in Production Systems   | · · · · · 17 |  |

| Chapter 3. Architectural Model               | 21           |  |

| 3.1 Basic Definitions                        | 22           |  |

| 3.2    | System Overview                                        | 27 |

|--------|--------------------------------------------------------|----|

|        | 3.2.1 Detailed Processor Model                         | 32 |

|        | 3.2.2 Conflict Set Management                          | 34 |

|        | 3.2.3 Broadcasting Interconnection Network Arbitration | 38 |

| 3.3    | Correctness of the Processing Model                    | 39 |

| Chapte | er 4. Benchmarking                                     | 47 |

| 4.1    | A Contemporaneous TSP                                  | 48 |

|        | 4.1.1 A Production System Solution for CTSP            | 49 |

| 4.2    | Confusion of Patents Problem                           | 53 |

| 4.3    | The Hotel Operation Problem                            | 54 |

| 4.4    | The Game of Life                                       | 54 |

| 4.5    | The Line Labeling Problem                              | 55 |

| 4.6    | Benchmark Static Measures                              | 55 |

| Chapte | er 5. Production Partitioning Algorithms               | 57 |

| 5.1    | Production Relationship Graph                          | 58 |

| 5.2    | The Minimum Cut Problem                                | 60 |

| 5.3    | Algorithm 1                                            | 60 |

| 5.4    | Algorithm 3                                            | 64 |

| 5.5    | Algorithm 5                                            | 66 |

| 5.6    | Algorithm 6                                            | 68 |

| 5.7    | Simulation Results                                     | 69 |

| Chapte | e <b>r 6.</b> | Performance Evaluation through System Simulation 72                                                                                                                   | i  |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1    | Perfor        | mance Measurements                                                                                                                                                    | -  |

|        | 6.1.1         | Parallel Firing Speedup 74                                                                                                                                            | :  |

|        | 6.1.2         | Effectiveness of Associative Memories                                                                                                                                 | )  |

|        | 6.1.3         | Associative Memory Size                                                                                                                                               | ;  |

|        | <b>6.1.</b> 4 | Use of Bus 84                                                                                                                                                         | -  |

| Chapte | er 7.         | Rete Network with Multiple Functional Units 86                                                                                                                        | ;  |

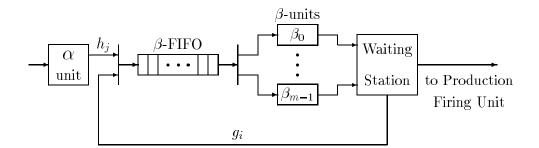

| 7.1    | Multij        | ple $\beta$ -Unit Rete Network                                                                                                                                        | ,  |

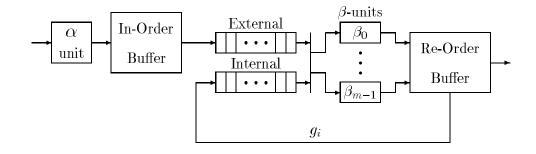

| 7.2    | Synch         | ronization Issues                                                                                                                                                     | ;  |

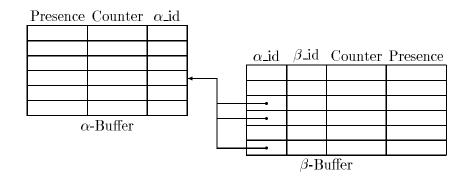

| 7.3    | In-Ore        | ler Buffer                                                                                                                                                            | )  |

| 7.4    | Re-Or         | der Buffer 95                                                                                                                                                         | )  |

| 7.5    | Exper         | imental Results                                                                                                                                                       | ,  |

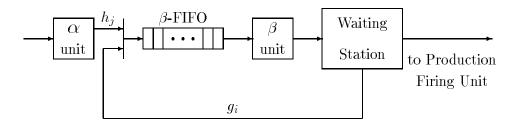

| Chapte | er 8.         | Analytical Model 100                                                                                                                                                  | )  |

| 8.1    | Single        | $\beta$ -Unit Architecture                                                                                                                                            | 2  |

| 8.2    | Multij        | ple $\beta$ -Unit Architecture $\ldots \ldots \ldots$ | ;  |

| 8.3    | Analy         | tical Model $\ldots \ldots 104$                                            | :  |

|        | 8.3.1         | Single $\beta$ -Unit Model                                                                                                                                            | )  |

|        | 8.3.2         | Multiple $\beta$ -Unit Model                                                                                                                                          | )  |

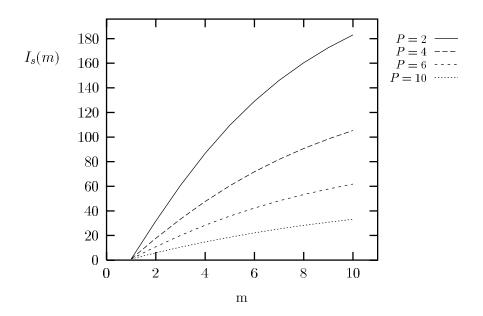

|        | 8.3.3         | Rete Processing Improvement                                                                                                                                           | 2  |

| 8.4    | Exper         | imental Results                                                                                                                                                       | ;  |

| 8.5    | Final         | Remarks                                                                                                                                                               | ;; |

| Chapte                                                 | er 9.          | Conclusion                                                          | 119 |

|--------------------------------------------------------|----------------|---------------------------------------------------------------------|-----|

| Appendix A. Performance Measurements                   |                | 122                                                                 |     |

| Appendix B. Study of CTSP Benchmark                    |                | 126                                                                 |     |

| Appendix C. Derivation of Analytical Model Expressions |                |                                                                     | 133 |

| C.1                                                    | Single         | $\beta$ -Unit Model                                                 | 133 |

|                                                        | C.1.1          | Generating Function for Single $\beta$ -Unit System $\ldots$        | 133 |

|                                                        | C.1.2          | Average Number of Tokens in a Single $\beta\text{-Unit System}$     | 137 |

| C.2                                                    | Multip         | ble $\beta$ -Unit Model                                             | 140 |

|                                                        | C <b>.2.</b> 1 | Generating Function for Multiple $\beta$ -Unit System               | 140 |

|                                                        | C <b>.2.</b> 2 | Average Number of Tokens in the Multiple $\beta\text{-Unit System}$ | 146 |

| Bibliography 14                                        |                | 149                                                                 |     |

Vita

**160**

# List of Figures

| 2.1         | Generic Production System Architecture                                          | 11 |

|-------------|---------------------------------------------------------------------------------|----|

| 2.2         | Section of a Rete Network                                                       | 13 |

| 3.1         | Parallel Machine Model                                                          | 29 |

| 3.2         | Processing Element Model                                                        | 33 |

| 3.3         | (a) Antecedents of Fireable Instantiation Memory; (b) Fireable                  |    |

|             | Instantiation Memory                                                            | 35 |

| <b>3.</b> 4 | Pending Matching Memory                                                         | 37 |

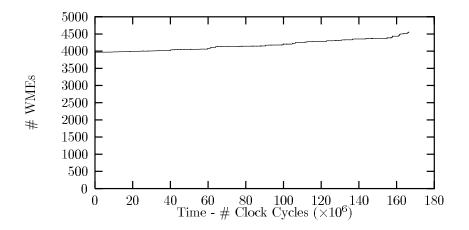

| 4.1         | Variation in the knowledge base size during the execution of moun2.             | 53 |

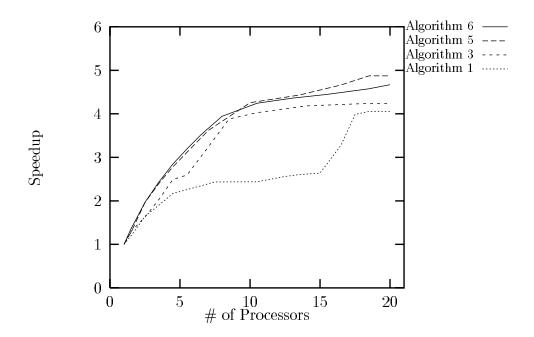

| 5.1         | Partition Algorithm Speedup Curves for south2                                   | 71 |

| 5.2         | Partition Algorithm Speedup Curves for patents                                  | 71 |

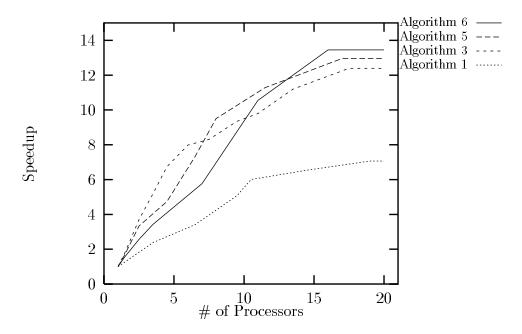

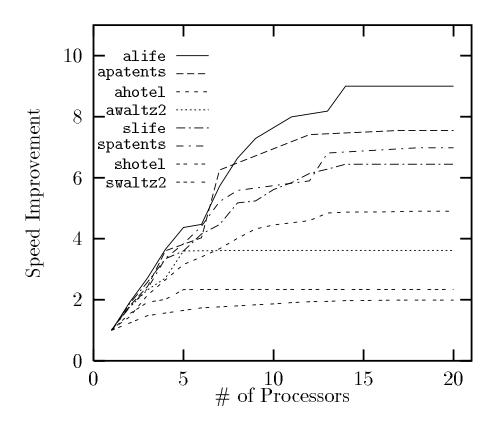

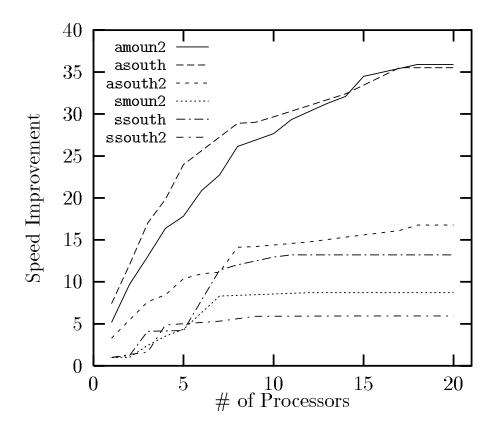

| 6.1         | Speed improvement obtained by proposed architecture (prefix <b>a</b> )          |    |

|             | and by a reference synchronizing architecture (prefix ${\bf s}){\boldsymbol .}$ | 76 |

| 6.2         | Speed improvement obtained by proposed architecture (prefix <b>a</b> )          |    |

|             | and by a reference synchronizing architecture (prefix ${\bf s}){\boldsymbol .}$ | 77 |

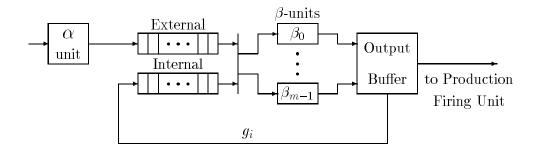

| 7.1         | Rete Network with $m \beta$ -Units                                              | 88 |

| 7.2         | Synchronizing Buffers in Rete Network with $m \beta$ -Units                     | 89 |

| 7.3         | Organization of In-Order Buffer (IOB)                                           | 93 |

| 7.4         | Organization of Re-Order Buffer (ROB)                                           | 96 |

| 8.1          | Single $\beta$ -Unit System                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------|

| 8.2          | System with $m \beta$ -Units                                                                                              |

| 8.3          | State Diagram for a Single $\beta$ -Unit System 106                                                                       |

| 8.4          | State Diagram for System with $m \beta$ -Units                                                                            |

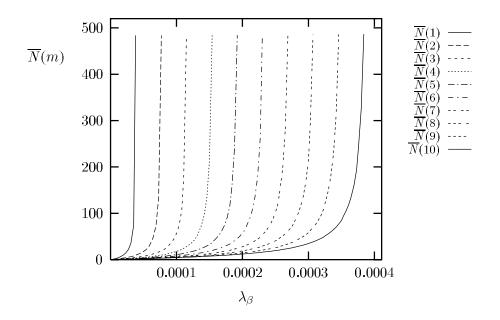

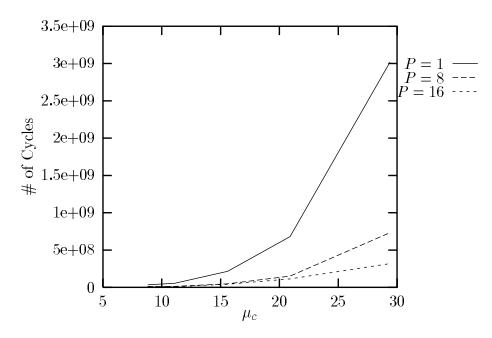

| 8.5          | Average Number of Tokens in the System versus $\lambda_{\beta}$ for moun2 in<br>a Single Processor Architecture           |

| 8.6          | Speed improvement prediction for moun2 considering $\lambda_{\beta}$ constant<br>for all values for $m. \ldots 115$       |

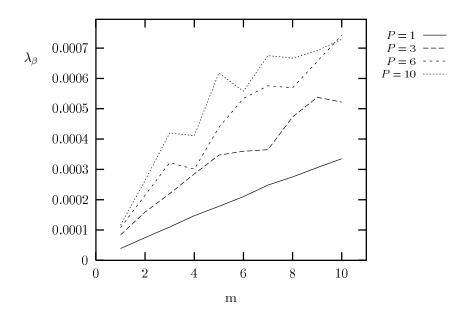

| 8.7          | Variation of $\lambda_{\beta}$ with <i>m</i> for moun2 ( <i>P</i> indicates the number of processors in the architecture) |

| 8.8          | Speed improvement prediction for moun2 considering that $\lambda_{\beta}$ changes<br>when more $\beta$ -units are used    |

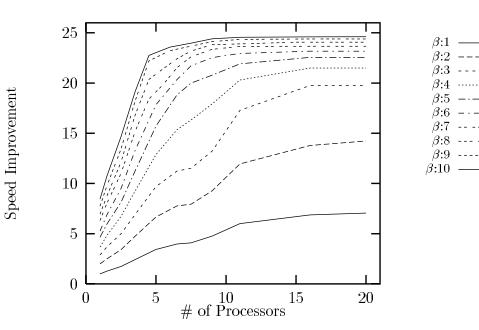

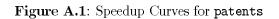

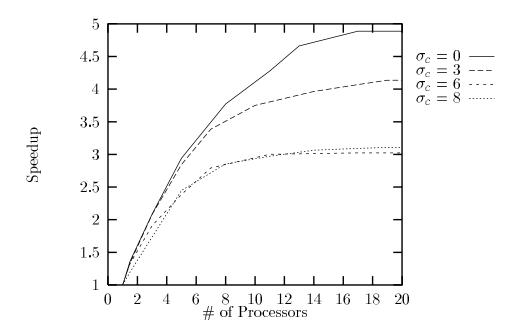

| A.1          | Speedup Curves for patents                                                                                                |

| A.2          | Speedup Curves for waltz2 123                                                                                             |

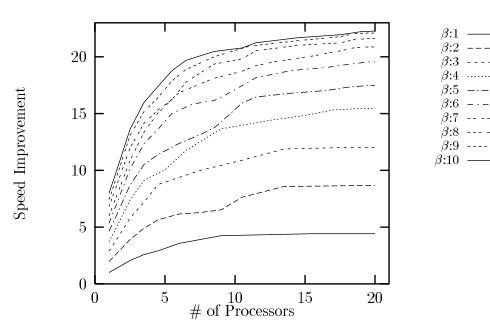

| A.3          | Speedup Curves for south                                                                                                  |

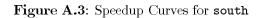

| A.4          | Speedup Curves for south2 124                                                                                             |

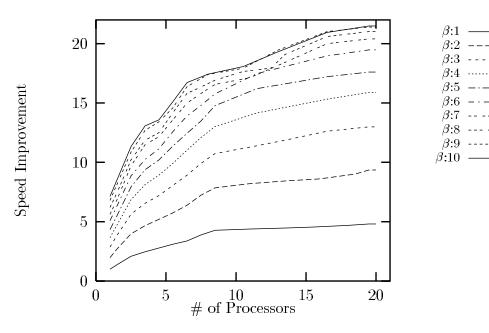

| A.5          | Speedup Curves for moun2                                                                                                  |

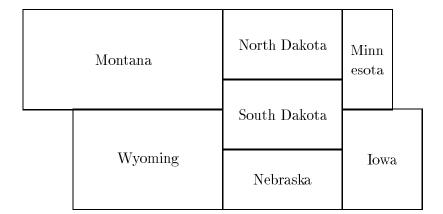

| B <b>.</b> 1 | Country map                                                                                                               |

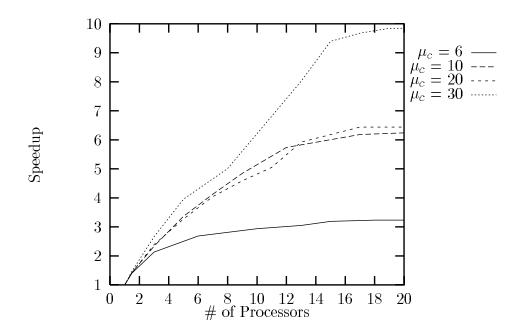

| B.2          | Speedup Curves for single $\beta$ -unit architecture ( $\sigma_c = 3$ ) 130                                               |

| B.3          | Speedup Curves for 10 $\beta$ -unit architecture ( $\sigma_c = 3$ ) 130                                                   |

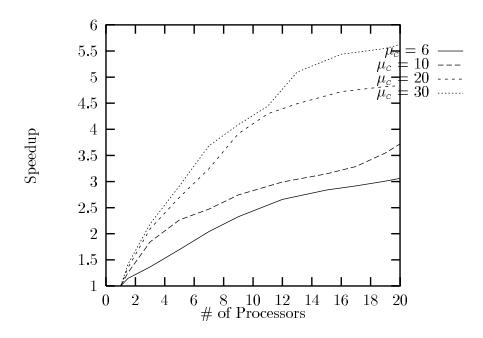

| B.4          | Speedup Curves for single $\beta$ -unit architecture( $\mu_c = 15$ ) 131                                                  |

| <b>B.</b> 5  | Speedup Curves for 10 $\beta$ -unit architecture ( $\mu_c = 15$ ) 131                                                     |

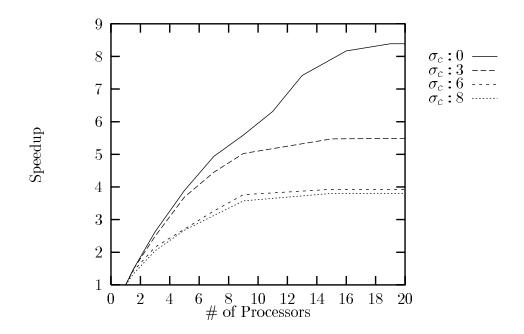

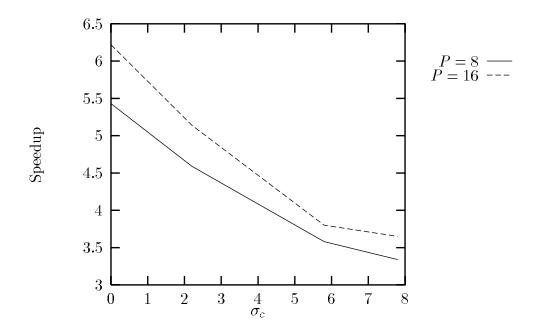

|             | ation in the number of cities $\sigma_c$ ( $\mu_c = 15$ )               |

|-------------|-------------------------------------------------------------------------|

| <b>B.</b> 6 | Speedup for single $\beta$ -unit architecture versus the standard devi- |

# List of Tables

| 2.1         | Measures by Nayak <i>et al.</i>                                     | 18  |

|-------------|---------------------------------------------------------------------|-----|

| 2.2         | Read-Write ratio $(R_{rw})$ estimates based on the study by Nayak   |     |

|             | <i>et al.</i>                                                       | 19  |

| 2.3         | Surface measurements by Gupta and the corresponding $R_{rw}$ es-    |     |

|             | timates                                                             | 20  |

| 3.1         | Possible dependencies between $R_n$ and $R_m$                       | 46  |

| 4.1         | Static measures for the CTSP benchmark according to $C$ and $\mu_c$ | 52  |

| 4.2         | Static measures for benchmarks used                                 | 56  |

| 6.1         | Speed improvement over synchronized architecture using the same     |     |

|             | number of processors.                                               | 78  |

| 6.2         | Speedup due to use of CAMs <sup>1</sup>                             | 82  |

| 6.3         | Maximum and average "crest" for memory size (bytes)                 | 84  |

| <b>6.</b> 4 | Percentage of time that the bus is busy                             | 85  |

| 7.1         | Speedups of a concurrent production system with multiple $\beta$ -  |     |

|             | functional units.                                                   | 98  |

| 7.2         | Speedups of a concurrent Production System with multiple $\beta$ -  |     |

|             | functional units.                                                   | 99  |

| 8.1         | Parameter Measurements for moun2                                    | 113 |

| B <b>.</b> 1 | Specified and actual values for $\mu_c$ and $\sigma_c$ for the benchmarks |     |

|--------------|---------------------------------------------------------------------------|-----|

|              | studied in this appendix                                                  | 127 |

| B.2          | Distribution of number of cities per state.                               | 128 |

# List of Abbreviations and Acronyms

| BIN            | Broadcasting Interconnection Network          |  |

|----------------|-----------------------------------------------|--|

| BNB            | Broadcasting Network Buffer                   |  |

| $\mathbf{CAM}$ | Content Addressable Memory                    |  |

| $\mathbf{CE}$  | Condition Elements                            |  |

| CTSP           | Contemporaneous Traveling Salesperson Problem |  |

| DNT            | Dependent on Network Transactions             |  |

| FIC            | Firing Instantiation Controller               |  |

| FIFO           | First-In First-Out                            |  |

| FIM            | Firing Instantiation Memory                   |  |

| I/OP           | Input Output Processor                        |  |

| $\mathbf{IC}$  | Instantiation Controller                      |  |

| IFE            | Instantiation Firing Engine                   |  |

| INT            | Independent of Network Transactions           |  |

| IOB            | IOB In-Order Buffer                           |  |

| LHS            | Left Hand Side                                |  |

| ME             | Matching Engine                               |  |

| $\mathbf{PC}$  | Production Controller                         |  |

| $\mathbf{PMM}$ | Pending Matching Memory                       |  |

| $\mathbf{PM}$  | Production Memory                             |  |

| PRG            | Production Relationship Graph                 |  |

| $\mathbf{PS}$  | Production System                             |  |

| RAM            | Reference Addressable Memory                  |  |

| RHS            | Right Hand Side                               |  |

| IIII           | Right Halla blac                              |  |

| ROB           | Re-Order Buffer               |

|---------------|-------------------------------|

| $\mathbf{SD}$ | Snooping Directory            |

| TSP           | Traveling Salesperson Problem |

| VLSI          | Very Large Scale Integration  |

| WME           | Working Memory Element        |

|               |                               |

# List of Symbols

### Chapter 3

| $R_{rw}$          | — Read-write ratio.                                            |

|-------------------|----------------------------------------------------------------|

| $R_i$             | — $i^{th}$ production.                                         |

| $A(R_i)$          | — Set of antecedents of production $R_i$ .                     |

| $C(R_i)$          | — Set of consequents of production $R_i$ .                     |

| $W_k$             | — $k^{th}$ Working Memory Element.                             |

| $T[W_k]$          | — Type of Working Memory Element $W_k$ .                       |

| $S_{A(R_i)}[W_k]$ | — Sign of Working Memory Elements of type $T[W_k]$ in the an-  |

|                   | tecedents of production $R_i$ .                                |

| $S_{C(R_i)}[W_k]$ | — Sign of Working Memory Elements of type $T[W_k]$ in the con- |

|                   | sequents of production $R_i$ .                                 |

| $P_i$             | — $i^{th}$ processor in the parallel architecture.             |

| $\mathcal{I}$     | — A collection of production instantiation.                    |

## Chapter 4

| K               | — A continent.                                                                       |

|-----------------|--------------------------------------------------------------------------------------|

| $C_i$           | — The $i^{th}$ country in the continent.                                             |

| $P(C_i)$        | — Predecessor of country $C_i$ in a continent tour.                                  |

| $S(C_i)$        | — Successor of country $C_i$ in a continent tour.                                    |

| $b(C_i, C_j)$   | — Center of the border between consecutive countries $C_i$ and                       |

|                 | $C_j$ .                                                                              |

| $\mu_c$         | — Average number of cities per country.                                              |

| $\sigma_c$      | — Standard deviation for number of cities per country.                               |

| m(i)            | — Number of cities in the $i^{th}$ country.                                          |

| $C_{\pi(i)}$    | — The $i^{th}$ country to be visited in a tour.                                      |

| $c_{i,\tau(j)}$ | — The $j^{th}$ city to be visited in the tour of the $i^{th}$ country.               |

| d(ck, i, cl, j  | ) — distance between $i^{th}$ city of $k^{th}$ country and $j^{th}$ city of $l^{th}$ |

#### country.

### Chapter 5

| R                  | — Set of vertices in Production Relationship Graph (PRG).        |

|--------------------|------------------------------------------------------------------|

| $R_i$              | — The $i^{th}$ vertex in PRG. It represents production $R_i$ .   |

| E                  | — Set of all edges of PRG.                                       |

| $E_{ij}$           | — The edge connecting $R_i$ and $R_j$ in PRG.                    |

| $w(E_{ij})$        | — Weight of edge $E_{ij}$ of PRG.                                |

| $S_k$              | — The $k^{th}$ subset of edges of PRG.                           |

| $cc(R_i)$          | — Cut cost of vertex $R_i$ .                                     |

| $W(R_i)$           | — Cumulative weight of vertex $R_i$ .                            |

| a                  | — Maximum number of antecedents in any production.               |

| С                  | — Maximum number of consequents in any production.               |

| N                  | — Number of productions in a production system program.          |

| $F(R_i, S_k)$      | — Fitness of vertex $R_i$ to subset $S_k$ .                      |

| n                  | — Number of processors in the architecture or number of parti-   |

|                    | tions to be generated by a partition algorithm.                  |

| $\mathcal{L}(S_i)$ | — Work load of subset $S_i$ .                                    |

| $\mathcal{B}(R_j)$ | — Average number of beta tests performed for production $R_j$ in |

|                    | previous runs.                                                   |

| $B(S_i)$           | — Number of beta tests expected to be performed for produc-      |

|                    | tions in set $S_i$ .                                             |

## Chapter 8

| m             | — Number of $\beta$ -units in the Rete Network.                    |

|---------------|--------------------------------------------------------------------|

| $S_{Rete}(m)$ | — Speedup of Rete Network with $m \beta$ -units.                   |

| $T_{lpha}$    | — Average amount of time spent in $\alpha$ -nodes.                 |

| $T_{eta}(m)$  | — Average amount of time spent in $\beta$ -nodes in a Rete Network |

|               | with $m \beta$ -units.                                             |

| $eta_i$       | — $i^{th} \beta$ -node in a Rete Network.                          |

| $\mathcal{B}$ | — Set of all $\beta$ nodes in a Rete Network.                      |

| $\mathcal{S}(eta_i)$       | — Signal of the antecedent associated with $\beta_i$ .                           |

|----------------------------|----------------------------------------------------------------------------------|

| $\mathcal{C}(eta_i,eta_j)$ | — Indicates possible conflict among tokens directed to $\beta_i$ and $\beta_j$ . |

| $\mathcal{T}$              | — Set of all tokens processed in a Rete Network.                                 |

| $T_i$                      | — The $i^{th}$ token processed in a $\beta$ -node.                               |

| $\mathcal{A}(T_i)$         | — Indicates the action of token $T_i$ (add or delete).                           |

| $h_j$                      | — Probability that an $\alpha$ -node produced a bulk of $j$ tokens to            |

|                            | deliver to $\beta$ -node processing.                                             |

| H(z)                       | — Generating function for the $h_j$ .                                            |

| $\overline{H}$             | — First moment of $h_j$ .                                                        |

| $\overline{H^2}$           | — Second moment of $h_j$ .                                                       |

| $g_i$                      | — Probability that the processing of a token in a $\beta$ -node pro-             |

|                            | duces $i$ new tokens.                                                            |

| G(z)                       | — Generating function for the $g_i$ .                                            |

| $\overline{G}$             | — First moment of $g_i$ .                                                        |

| $\overline{G^2}$           | — Second moment of $g_i$ .                                                       |

| $\lambda_eta$              | — Arrival rate at $\beta$ -units.                                                |

| $\mu_eta$                  | — $\beta$ -unit processing rate.                                                 |

| $p_k$                      | — Probability that $k$ tokens are present in the $\beta$ portion of the          |

|                            | Rete Network, including the tokens being processed.                              |

| P(z)                       | — Generating function for the $p_k$ .                                            |

| $ ho_1$                    | — Utilization rate for a single $\beta$ -unit Rete Network.                      |

| $ ho_m$                    | — Utilization rate for an $m$ - $\beta$ -unit Rete Network.                      |

| $\overline{N}(m)$          | — Average number of $\beta$ -tokens in a Rete Network with $m \beta$ -           |

|                            | units.                                                                           |

| $\overline{T}(m)$          | — Average time to process a $\beta\text{-token}$ in a Rete Network with $m$      |

|                            | $\beta$ -units.                                                                  |

|                            |                                                                                  |

#### Chapter 1

## Introduction

"... I believe that at the end of the century the use of words and general educated opinion will have altered so much that one will be able to speak of machines thinking without expecting to be contradicted." (Alan Turing, 1950) [87] as quoted in [34].

When Alan Turing proposed a general purpose machine, the word *computer* was typically used to designate a person, usually a number crunching clerk, whose function was to perform computations. Although Turing envisioned the use of a general purpose machine to free clerks from their tedious tasks, his long term goal and motivation was the construction of a *thinking machine*. After many years of theoretical and practical work, including important contributions to the construction of code-breaking machines that were key in the victory of the allied forces in World War II, Alan Turing abandoned the field of computing machine construction, predicting that by the turn of the century humankind

would have constructed a machine that could be regarded as a *thinker* [87].

Much has changed since the days when Gödel showed the incompleteness of arithmetic and Alan Turing and Alonzo Church were pondering Hilbert's *Entscheidungs-problem*. Hilbert had asked "Can mathematics be complete, consistent and decidable?" [34, 35]. While Church used lambda-calculus to tackle the problem, Turing conceived of a theoretical device, now famous as a *Turing machine*. Speculating about the numerous possibilities brought about by such machines, Turing posed the question "Can machines think?" This very question widened and rekindled old philosophical indagations about the meanings of "thinking" and of "being intelligent" [12, 66]. Turing's question is still unanswered and it remains a distant goal of humankind either to construct a thinking machine or to prove that such a machine cannot be constructed. Computer scientists and knowledge experts are still developing techniques that could eventually lead to a thinking machine. Meanwhile, philosophers continue to ponder the possibility of deciding whether such machines are indeed thinking.

As Turing indicated, the meaning of words change over time and even more so in periods of fast technological advances. For instance, the ready availability of computers in the second half of this century has influenced models of thought [9]. The transformation of Turing's dream into a scientific discipline required a narrow view of intelligence [76]. Although still quite far from the goal of constructing a thinking machine, the study of Artificial Intelligence (AI) has progressed in two directions: "Pure" AI is concerned with knowledge representation and with the construction of machines that mimic human intelligence; "Applied" AI tries to construct artificial systems that perform tasks that are assumed to require human intelligence, but does not concern itself with the ways these tasks are accomplished [47]. Studies in applied AI have branched into many areas of research such as knowledge systems [31], genetic and evolutionary algorithms [24, 25, 36], fuzzy systems [94], neural networks [33], interactive agents [57, 68], and asynchronous organization [17], just to name some.

In the area of knowledge representation and processing, Production Systems are predominant structures. In such systems, knowledge is represented in the form of statements about a given knowledge domain in which the system operates. The collection of all statements form a knowledge base. A set of productions, also called rules, specify changes to this knowledge base according to its current state. The productions to be executed are selected by the inference engine and their actions alter the knowledge base accordingly. This dissertation addresses the problem of building a computer architecture that implements Production Systems.

Early experiments with Production Systems followed the pure branch of AI: the interest was centered on reproducing "simple" human activities in a computer to understand how these activities are performed in the human brain. Scientists chose to investigate activities that are easily performed by a fouryear-old child, such as building a pile of blocks. Early results were disastrous because the scientists had failed to "teach" their machine basic notions of space and gravitation law. As a result, the machine would start building the pile by trying to place the top block first [65]. These early experiments led scientists to understand that a great amount of common-sense knowledge is involved even in the most simple tasks. It was also observed that knowledge based systems would be much easier to build in restricted knowledge domains.

This underestimation of the importance and complexity of *common-sense* knowledge reflects the fact that people tend to regard as simple and trivial knowledge that has been acquired a long time in the past [57]. This phenomenon is observed at the individual level and at the species level. For instance, a concept that seems difficult for a freshman is regarded as elementary by the same student in his senior year. At the species level, in the end of the twentieth century concepts such as quantum mechanics, fractals, quarks and black holes are understood only by a selected group of scientists. On the other hand, children understand currently accepted concepts such as the shape of the Earth and its movement, while the best scientists of the fifteenth century rejected these very ideas.

The initial failure with seemingly easy tasks motivated scientists to look for activities confined to a controlled environment where "common-sense knowledge" would not play such an important role as in a child's playground. This search pointed to the activities of experts, such as medical diagnosis, chemical analysis, computer system configuration, and airline routing planning. To the surprise of some, many expert activities were very suitable to be codified into a small set of rules. Such realizations lead to the birth of the *expert system* or *knowledge based system* area of research. The developments in this area transformed what started as pure AI study into an applied one: today the interest is centered on the extraction of knowledge from an expert to reproduce the task in a computer.

When a knowledge based system is used as an expert system that manipulates a number of "rules," it is also called a *rule-based system*. Production systems are commonly used to implement rule-based systems. When the inference engine of a production system is used to derive new knowledge from a set of basic facts or axioms, the system is called a *theorem proving system*.

A production system inference engine is said to use *forward chaining* or

forward inference when the system starts in an initial state and executes enabled productions to move to the final state. A *backward chaining* system starts at the goal state and tries to find the possible conditions that resulted in that state. Backward systems are often used for theorem proving while forward systems are common in expert systems [67]. In this research we study production systems with forward inference engines.

The investigation of new computer architectures for Production Systems is motivated by the unique characteristics and resource needs of such systems. First, the execution of Production Systems requires an impressive amount of searching. Second, most of the data manipulated by Processing Systems is symbolic. Because of these characteristics, execution of Production Systems in general purpose computers have failed to deliver the speed required by many industrial and commercial activities.

Chapter 2 presents a generic architecture for Production System that emphasizes the matching engine. Most of the previous research in the area has concentrated on the matching phase of the system. The presentation of the Rete Network is followed by a discussion of this early work, as well as an analysis of current trends of research. A survey of some previous experimental work is given to show that, in production systems, data is accessed much more often than it is modified.

The presentation of a concurrent production system architecture in Chapter 3 is preceded by a number of important definitions. This novel architecture consists of a small number of powerful processors that implement a parallel production system without global synchronization. After providing a detailed description of the architecture and processing model, we present a proof that the proposed architecture produces correct results under the serializability criterion.

The absence of a comprehensive set of benchmarking tools is a well-known weakness of production system research. Chapter 4 presents a new benchmarking facility that is a modification of the Traveling Salesperson Problem. The great advantage of this benchmark is that it allows for variation in the number of productions, database size, ratio between local and global data, and size of local data clusters. Chapter 4 also describes and presents static measures for other performance evaluation benchmarks.

Chapter 5 studies the problem of partitioning productions among processors in a parallel machine. All the partition algorithms presented have a common set of goals: minimizing the duplication of working memory elements, reducing traffic in the bus, and balancing the amount of processing in each processor. Our experiments indicate that dynamic algorithms that consider the firing frequency of each production perform better than algorithms based exclusively on static information.

In Chapter 6, system simulation is used to measure performance. The most salient innovations in the new architecture are the elimination of global synchronization to resolve the conflict set and the overlapping between the matching and the select-act phases of production systems. The performance of the new architecture is compared to that of a synchronizing architecture that does not allow overlapping between production system phases. Other measures presented in this chapter include the following: measures for effectiveness of associative memories, estimates for memory size, and level of activity in the bus.

The evaluation of the architecture through system simulation in Chapter 6 indicated that the bottleneck in the architecture execution is in the processing of tokens in the  $\beta$ -nodes of the Rete Network. In Chapter 7 we extend the architecture by allowing the use of a multiple functional  $\beta$ -unit Rete Network

within each processor. Performance measurements indicate that considerable speedup is obtained with a modest number of additional functional units.

The ability to predict the benefits of a new device without constructing or simulating it, facilitates the process of designing a new computer architecture. Chapter 8 develops an analytical model based on queueing theory to predict the amount of performance improvement obtained in a Rete Network with m functional units.

The introduction of this novel architecture delivers performance improvements beyond what was thought possible just a few years ago. We hope that these results can inspire new research which will eventually lead to the construction of faster production system machines. A broader use of expert systems in commerce, industry, and services would release human experts from tedious activities and result in more efficient, safe, and cost-effective processes.

The slow advance since Turing's days indicates that progress towards the construction of a thinking machine might be counted in centuries rather than in years as Turing had anticipated. Moreover, because expert systems are brittle and only operate in a narrow area of structured knowledge, they have a very limited capability for knowledge representation, [32, 65]. Considered as a pure AI technique and viewed against the backdrop of the human enterprise to construct a thinking machine, production systems are just a "sliver" that might be forgotten in some fringe of history.

However, if production systems are viewed as an applied AI technique, they already have a successful history. The integration of databases with expert systems creates an ever increasing demand for faster machines that can execute production systems with large knowledge bases [31, 84]. Production Systems have also been integrated with other AI technologies to deliver adaptive support systems [18]. Systems that for a long time seemed a mere academic curiosity such as medical diagnosers [10] are now delivering advisory services and reducing the cost of health care [14]. Expert systems have been replacing expensively trained human experts in many areas for more than fifteen years: a 1984 inventory reported over one-hundred thirty systems built [56] while a 1992 article list more than eighty vendors of tools to help design expert systems [84].

### Chapter 2

## Background

Considerable efforts have been made towards speeding up production system machines in the past twenty years [6, 52]. Originally, production systems were realized as interpreted language programs for sequential machines. The high cost of matching motivated the development of concurrent matching systems and, subsequently, systems that also allowed multiple productions to be fired at the same time. In a separate line of research, modern compile optimization techniques were developed to run production system programs more efficiently on general purpose sequential machines.

These efforts have led to great advances in the understanding of the issues involved in the construction of faster production system machines, but only limited improvement in actual performance. Also, there have been few attempts to integrate progress made in different areas: the use of the restrictive commutativity criterion for correctness and the notion of a match-select-act "cycle" forced even advanced architectures to perform synchronization before each production firing; compile optimization techniques were mostly restricted to sequential machines; many of the concurrent matching engines were constructed with a large number of small processors and were not combined with parallel firing techniques. Moreover, parallel processing researchers failed to take advantage of the fact that, in typical production systems, reading operations are performed much more often than writing ones.

#### 2.1 A Generic Production System Architecture

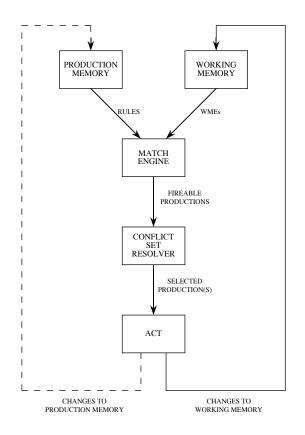

Most of the research towards speeding up expert systems uses the architectural model represented in Figure 2.1. The memory of the system is divided into a set of productions or rules stored in the production memory, and a set of facts stored in the working memory. The working memory gets its name from the fact that it is used as a "scratch" memory where the system writes and overwrites partial results. Each fact of the knowledge domain is stored in this memory as a unit called a Working Memory Element (WME).

A production stored in the production memory consists of a set of conditions and a set of actions. In a forward chaining system, the productions are usually syntactically expressed with the conditions positioned to the left of an arrow. Therefore, the conditions are called the Left Hand Side (LHS) of the production. Similarly, the assertions or actions, positioned to the right of the arrow, are called the Right Hand Side (RHS) of the production. Some research groups have adopted a nomenclature that is adequate for both forward and backward chaining systems [16]. They label the conditions the *antecedents* of the production and the assertions the *consequents* of the production.

A production in the production memory is said to be *fireable* if all its nonnegated conditions are satisfied and none of its negated conditions is satisfied.

Figure 2.1: Generic Production System Architecture

Also, if variables appear in more than one condition element, all instantiations of the same variable must be bound to the same value. The match engine compares (or matches) all conditions of all productions in the production memory against all facts in the working memory, while keeping track of variable bindings to check which productions are fireable. The set of all fireable productions at the end of the match processing is called the *conflict set*. The conflict set resolver decides which production is selected to fire in the current cycle. Criteria used to select the winning production include: recency, specificity, priority, and context. After a production is selected to fire, the act phase of the system produces changes in the memory, creating or deleting WMEs. Most production systems generate changes that affect only the Working Memory, altering the facts in the knowledge base. Some systems also generate new productions or eliminate old ones. We suggest that such systems be called *adaptive expert systems* [39] or *learning expert systems*, because they have the capability of adapting to changes in the environment.

#### 2.2 The Matching Engine

The amount of work performed by the matching engine is a combinatorial function of the number of productions in the system and the number of facts in the knowledge base. However, two characteristics of production systems allow an efficient solution to this problem: distinct productions have identical condition elements and pieces of knowledge stored in the working memory of a production system change slowly over time. The slow change in the knowledge base implies that if the results of the matching in one cycle are saved for the next cycle, a substantial amount of work can be eliminated. The existence of productions with identical antecedents allows the construction of an algorithm in which the results of matching shared conditions are used by all productions that need it.

The best-known state saving algorithm is the Rete Network created by Forgy [20]. Forgy reports that Rete is inspired by the *Pandemonium* machine of Self-ridge [74]. Pandemonium was one of the earliest learning machines and consisted of multiple layers of *demons*. A demon in a given level supervised an inferior level of demons. When it observed meaningful patterns, it sent messages to a superior level. The top-level demons performed more telling actions.

The Rete Network is a data-flow graph that encodes the antecedents of productions. The inputs to the Rete Network are changes to the working memory generated in the act phase of one cycle, and the outputs of the network are changes to the conflict set used to choose a production to be fired in the next cycle. The following discussion of Rete Networks is presented here after Gupta and Forgy [27, 29], Lee and Schor [53], and Miranker [58].

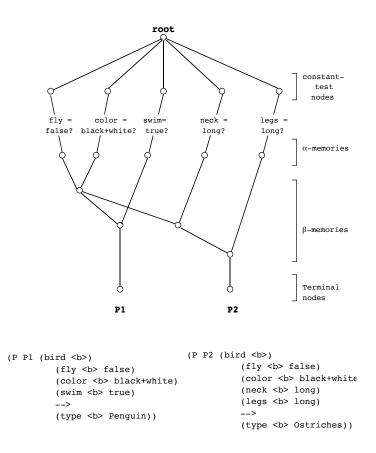

Figure 2.2: Section of a Rete Network

Figure 2.2 presents a Rete Network with the set of production antecedents encoded in it. The network is formed by four different kind of nodes: constanttest nodes, memory nodes, two-input nodes and terminal nodes. The constanttest nodes appear in the first layer of the network. They store attributes that have constants in the value field and perform intra-condition tests to determine if a working memory element satisfies these constant fields of the condition element. In the original Rete Network, the result of this test was stored in a local  $\alpha$ -memory [29]. Some authors claim that the  $\alpha$ -memories can be eliminated because the constant test takes a negligible amount of time [53]. In this case the one-input nodes are called  $\alpha$ -nodes and are memoryless.

Two-input nodes, also called *and*-nodes, *join*-nodes, or  $\beta$ -nodes, perform the matching between distinct condition elements. A  $\beta$ -node has one memory associated with each input. A token arriving in a  $\beta$ -node come either from another  $\beta$ -node or from an  $\alpha$ -node. Whenever a new token arrives in one of a node's inputs, it is compared with all tokens present in the other side memory. Good hashing techniques are necessary to speed up the matching in the twoinput nodes. Otherwise, it might be necessary to process long lists of tokens. [27].

Performance evaluation, modifications, and improvements of Rete are found in the works of Gupta [27, 29], Lee & Schor [53], Stolfo [80], Kelly and Seviora [42, 43], Gaudiot and Sohn [23, 78], and Barachini & Theuretzbacher [7]. Miranker proposed a useful modification to the traditional Rete Network in which intermediate memory nodes are eliminated. This modified Rete is called Treat [58].

A study by Gupta [27] motivated extensive research on concurrent matching. Gaudiot and Sohn [23, 78] proposed a data-driven machine with parallel matching. They advocated the suitability of data-flow machines for the processing of production systems. Kelly and Seviora [42, 43] proposed a multiprocessor architecture that supports comparison level partitioning and consists of a matching multiprocessor attached to a host computer. Rowe *et al.* [8, 69] developed METE/PIPER, an extension of Rete to explore intra-production parallelism in match processing and conflict resolution. Other noteworthy parallel implementations of Rete appear in [3, 30, 39, 52, 80, 81, 73].

#### 2.3 Current Research and Trends

Parallel firing systems is a current research topic that The ability to fire productions in parallel introduces some new issues such as the identification of dependencies among productions. Kuo and Moldovan [50, 51] Schmolze [71], Kuo *et al.* [49], and Xu and Hwang [92] have worked in this area and suggested solutions to ensure the correctness of a parallel firing engine operation. The partitioning of production among processors also becomes an important issue in parallel firing systems. Oflazer [64], and Xu and Hwang [92] presented some interesting results in this area. In most of the research geared towards parallel firing of productions, it is assumed that there is a synchronization point before each production fires, that is, no production firing takes place until all matching activities are completed.

There is no agreement on a good criterion to establish correctness of a parallel production system. Some researchers claim that serializability imposes too heavy a burden on the programmer, and suggest the use of a commutativity criterion that restricts the available parallelism even more [38]. Other researchers suggest that the serializability criterion is already too restrictive and argue the use of control structures tailored to each problem [62, 63]. A very recent work by Schmolze proposes the concept of a convergent production set in which serializability provides complete control of the final result. In such a system serializability is certainly enough to guarantee correctness [72]. An study of serializability as a correctness criterion based on a transaction model for parallel rule firing can be found in Srivastava et al. [79]. There is yet a third school of thought that advocates a meta-rule mechanism to allow the designer of the system to specify explicitly the control structure [83].

The elimination of synchronization in parallel production systems follows a trend of research in other areas of systems architecture, such as the development of A-Teams and scale-efficient organizations [17, 60, 85]. We anticipate that some results from these areas might be useful in improving execution of production systems. In this research we wager that the serializability criterion is a winner.

Acharya and Tambe have obtained impressive speed increases in the matching phase of production systems by means of storing collections of WMEs instead of single WMEs in the Rete Network [2]. Gordin and Pasik explored the use of set-oriented constructs as a means to integrate database management systems (DBMS) and rule-based systems [26]. Wu and Browne proposed the use of setoriented constructions in an object-based model for parallel rule-based systems, their goal is to increase concurrency [91]. An expansion on the use of collections to construct a parallel firing, asynchronous, collection-oriented system is still to be further studied. It is certainly a promising idea.

Another important area of research is in Production Systems languages and design aid tools. Murthy [60] correctly points out that for some problems, it is possible to gather a few hundred heuristics and put together a production system in a few weeks. However, maintaining these systems during their lifetimes might be very expensive. One example is the R1 system at DEC that at one time required a few hundred people for its maintenance. Good software engineering techniques need to be adopted in the construction of production systems to avoid such situations.

### 2.4 Read-Write Ratio in Production Systems

This section analyzes some published research to determine the expected read-write ratio in production systems. We are interested in learning the number of WMEs read for each WME modification performed. This ratio is important in evaluating the possibility of using a broadcasting network as an interconnection mechanism in a multiprocessor production system machine.

In a comparative study between Rete and Treat, Nayak *et al.* [61] measures the number of productions, the number of condition elements per production, the number of PS cycles executed, and the number of addition and deletion of WMEs reproduced on Table 2.1. The benchmarks in this table are the Eight Puzzle (EP), the Missionaries and Cannibals (M&C), R1 Soar, and Neomycin-Soar (NM). EP and M&C are toy programs, R1-Soar is an implementation of a subset of the system R1 that configures computer systems for DEC, implemented in Soar, and Neomycin-Soar is an implementation of a portion of Neomycin in Soar. Neomycin diagnoses infectious diseases like meningitis. The authors call attention to the fact that in a Soar program there is an average of 9 condition elements per production, compared with an average of 3 in OPS5 programs.

We examine these results to estimate how many reads are there for each write. In other words, how many antecedents are tested for each action taken on the consequents of a production. Therefore we define the *Read-Write Ratio*  $R_{rw}$ , as follows:

| Benchmark | # Prod. | $\frac{CEs}{Prod}$ | # Cycles  | Add.      | Del.      |

|-----------|---------|--------------------|-----------|-----------|-----------|

| EP        | 71      | 8.8                | 796       | $1,\!715$ | $1,\!313$ |

| M&C       | 78      | 8.9                | $1,\!617$ | $6,\!609$ | $5,\!620$ |

| R1-Soar   | 334     | 9.9                | $3,\!732$ | 7,810     | $6,\!458$ |

| NM        | 419     | 8.8                | $2,\!173$ | 4,554     | 4,336     |

Table 2.1: Measures by Nayak et al.

$$R_{rw} = \frac{\# reads}{\# writes} = \frac{\# WMEs \, probed}{\# WMEs \, added + \# WMEs \, deleted}$$

(2.1)

Table 2.2 shows numbers computed based on the results published by Nayak et al. The total number of writes in the first column is just the sum of the number of WMEs written and the number of WMEs read. If changes to the Working Memory use modify operations (like in OPS5) the number of writes tend to be smaller. If no modify operation is available, a modification needs to be implemented by a delete followed by an add operation. The total number of Condition Elements in the program was computed just by multiplying the average number of CEs per production by the number of productions. We assume that the conflict set is generated from scratch every time, therefore the total number of reads is equal the total number of CEs multiplied by the number of cycles that takes for the system to reach a state with the solution. This implies a very optimistic scenario where each WME is read only once in each cycle. The truly worst case has a complexity that is exponential in the number of antecedents in a production. The ratio  $R_{rw}$  varies between 100 and 1000, and is bigger for more "real life" problems. This number would be significantly smaller if the entire conflict set would not be generated before firing each production, or if some form of state saving is used. Even with such improvements, reads are

| Benchmark | Total $\#$ Writes | Total # CEs | Total $\#$ Reads | $R_{rw}$ |

|-----------|-------------------|-------------|------------------|----------|

| EP        | 3,028             | 625         | $497,\!500$      | 164      |

| M&C       | $12,\!229$        | 694         | 1,122,198        | 92       |

| R1-Soar   | 14,268            | $3,\!307$   | 12,341,724       | 864      |

| NM        | 8,890             | $3,\!687$   | 8,011,851        | 901      |

expected to significantly outnumber writes.

**Table 2.2**: Read-Write ratio  $(R_{rw})$  estimates based on the study by Nayak *et al.*

Perhaps the most important measurement study on production systems to date was published as the Ph.D. dissertation of Anoop Gupta [28]. He measured six production systems: R1, a program for configuring VAX computer systems; XSEL, a program which acts as a sales assistant for VAX computer systems; PTRANS, a program for factory management; HAUNT, an adventure game program; DAA, a program for VLSI design; and SOAR, an experimental problem solving architecture implemented as a production system. Gupta calls "surface measurement" the measures that one can do using exclusively the text of a production system without concern with the initial data base. Table 2.3 presents some of the surface measurements done by Gupta, as well as the  $R_{rw}$ computed by us.

Gupta presents the average number of actions and conditions per production, we compute the  $R_{rw}$  based on these numbers. Once more we assume that a conflict set is generated from scratch at every cycle, therefore the number of reads is given by the product of the number of productions and the average number of CEs per production. This measure is expected to be smaller in a parallel production system due to the partial decoupling among group of productions assigned to distinct processors. Also if the conflict set is not generated

| Benchmark | # Prod | $\frac{CEs}{Prod}$ | $\frac{Act}{Prod}$ | # types | $\frac{Attr}{CE}$ | $\frac{Vars}{CE}$ | $R_{rw}$  |

|-----------|--------|--------------------|--------------------|---------|-------------------|-------------------|-----------|

| R1        | 1,932  | 5.58               | 2.90               | 31      | 4.73              | 1.61              | $3,\!717$ |

| XSEL      | 1,443  | 3.84               | 2.41               | 36      | <b>3.6</b> 4      | 0.96              | 2,299     |

| PTRANS    | 1,016  | 3.12               | 3.64               | 81      | 4.11              | 2.14              | 871       |

| HAUNT     | 834    | 2.41               | 2.51               | 23      | 2.08              | 0.24              | 801       |

| DAA       | 131    | 3.91               | 2.86               | 20      | 3.89              | 2.69              | 179       |

| SOAR      | 103    | 5.80               | 1.83               | 12      | <b>3.</b> 78      | 1.70              | 326       |

**Table 2.3:** Surface measurements by Gupta and the corresponding  $R_{rw}$  estimates.

at every cycle, or if some state saving algorithm is used, the number of reads will be smaller. Gupta measures another interesting number, that is, the number of WME types in each benchmark (showed in Table 2.3 as number of types). This gives us an idea of the number of different "types" or classes of productions in the expert system and indicates the potential to partition the productions into independent sets.

The analysis of Nayak *et al.* and Gupta's experimental work confirms that the number of times that the knowledge base is probed is much higher than the number of times that it is modified. Such a situation suggests that a parallel architecture based on a broadcasting network with concurrent reading and exclusive writing operations might be an efficient design.

# Chapter 3

# **Architectural Model**

"Everything should be made as simple as possible, but not simpler." (Albert Einsten) as quoted in [57].

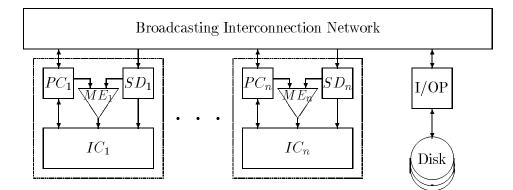

The architectural model proposed in this research consists of a moderate number of processors interconnected through a broadcasting network. The set of productions is partitioned among these processors with each production assigned to exactly one processor. A processor reads data only from its local memory, i.e., no read operations are performed over the network. Due to the absence of network reads and the low frequency of network writes, a simple bus should be adequate as the broadcasting system. This conclusion is supported by detailed experimental results showing the bus not to be a bottleneck even for a twenty processor system. A number of associative memories implement a system of lookaside tables to allow parallel operations in each processor, but allows the matchselect-act phases of a PS to overlap. A snooping directory isolates the activities in remote processors from the activities in a local processor, and interrupts a local operation only when pieces of data that affect the local processor are broadcast over the network.

Section 3.1 presents basic definitions that set the environment for the processing model. Section 3.2 introduces the architectural organization and expands on the processor model, conflict set management, and processor operation. Section 3.3 presents a theorem that demonstrates that the results produced by the processing model is correct according to the serializability criterion of correctness.

### **3.1** Basic Definitions

A Production  $R_i$  consists of a set of antecedents  $A(R_i)$  and a set of consequents  $C(R_i)$ : the antecedents specify the conditions upon which the production can be fired; the consequents specify the actions performed when the production is fired.

**Definition 3.1** The database manipulated by a Production System consists of a set of assertions. Each assertion is represented by a Working Memory **Element** (WME), notated by  $W_k$ . A WME consists of a class name and a set of attribute-value pairs that together characterize its type,  $T[W_k]$ .

**Consequence 3.1** Two WMEs of the same type are distinguished only by the values associated with their attributes.

**Definition 3.2** Each production antecedent specifies a type of WME and a set of values for its attribute-value pairs. A WME  $W_k$  is **tested** by an antecedent if it has the specified type. An antecedent is **matched** by a WME if the WME has the type specified and all the values in the antecedent match the ones in the WME.

**Definition 3.3** If the antecedents of a production  $R_i$  test WMEs of type  $T[W_k]$ , then  $W_k$  belongs to the antecedents of  $R_i$ , it is notated by  $W_k \in A(R_i)$ .

**Consequence 3.2** A WME might belong to the antecedents of more than one production.

**Definition 3.4** A non-negated antecedent tests for the presence of a WME in the memory. A negated antecedent tests for the absence of any matching WME in the memory. A production  $R_i$  is said to be fireable if all its non-negated antecedents are matched and none of its negated antecedents are matched.

The consequent of a production can specify three kinds of actions that modify WMEs: addition, deletion, or modification.

**Definition 3.5** A WME  $W_k$  belongs to the consequents of a production  $R_i$  iff the firing of  $R_i$  adds (deletes) any WME of type  $T[W_k]$  to (from) the Working Memory. This is denoted by  $W_k \in C(R_i)$ .

**Consequence 3.3** A WME might belong to the consequents of more than one production.

**Definition 3.6** If an antecedent of production  $R_i$  tests for the presence of a WME  $W_k$ , this is a **positive** test, notated by  $S_{A(R_i)}[W_k] = +$ , which is read as

" $R_i$  has at least one antecedent that tests for the presence of a WME of type  $T[W_k]$ ". In a similar fashion, if the test is for absence of  $W_k$ , it is a **negative** test, denoted by  $S_{A(R_i)}[W_k] = -$ .

**Definition 3.7** When the consequent of a production specifies the addition of a WME  $W_k$  to Working Memory, it is a **positive** action, denoted by  $S_{C(R_i)}[W_k] = +$ . A **negative** action specifies the deletion of a WME  $W_k$ , denoted by  $S_{C(R_i)}[W_k] = -$ .

**Consequence 3.4** The notation  $S_{A(R_i)}[W_k] \neq S_{C(R_j)}[W_l]$  implies that  $W_k \in A(R_i)$ ,  $W_l \in C(R_j)$ , and that  $R_i$  test of  $W_k$  is positive (negative) while  $R_j$  action on  $W_l$  is negative (positive).

**Consequence 3.5** A modify action is considered as a combination of two actions: a negative one that removes the old WME and a positive one that creates the modified WME.

In this model, productions are partitioned into disjoint sets with one set assigned to each processor.  $R_n \in P_i$  indicates that production  $R_n$  belongs to processor  $P_i$ . The Working Memory is distributed among the processors in such a way that a processor stores in its local memory all WMEs tested by its productions. This is stated in Axiom 3.1.

Axiom 3.1 (Condition for Ownership) A WME  $W_k$  is stored in the local memory of a processor  $P_i$  iff  $W_k \in A(R_n)$  and  $R_n \in P_i$ .

In the processing model discussed in section 3.2 some productions fire locally while others need to change WMEs that are stored in the local memory of remote processors. The following definitions describe important situations that appear in the execution of the model.

**Definition 3.8** A WME  $W_k$  is local to a processor  $P_i$  iff  $W_k$  is stored in the local memory of  $P_i$ ;  $W_k$  is not stored in the local memory of any other processor  $P_j$ ; and there is no production allocated to a processor other than  $P_i$  that changes  $W_k$ .

**Definition 3.9** A WME  $W_k$  is pseudo-local to a processor  $P_i$  iff  $W_k$  is stored in the local memory of  $P_i$ ;  $W_k$  is not stored in the local memory of any other processor  $P_j$ ; and there is at least one production allocated to  $P_j \neq P_i$  that changes  $W_k$ . We say that  $P_j$  shares  $W_k$ .

For example, a WME that is written by many processors and read by only one processor is *pseudo-local* for the processor that reads it; it is a *shared* WME for all processors that write it<sup>1</sup>. A processor does not stores shared WMEs in its local memory.

**Definition 3.10** A production  $R_n$  fires locally in a processor  $P_i$  iff  $\forall W_k \in C(R_n)$ ,  $W_k$  is local or pseudo-local to  $P_i$ .

**Consequence 3.6** A production that does not fire locally, is said to be a global **production**. Such a production must propagate actions to remote processors.

**Definition 3.11** A production  $R_n$  enables a production  $R_m$  iff  $\exists W_k$  such that  $S_{C(R_n)}[W_k] = S_{A(R_m)}[W_k]$ . A production  $R_n$  disables a production  $R_m$  iff  $\exists W_k$  such that  $S_{C(R_n)}[W_k] \neq S_{A(R_m)}[W_k]$ .

<sup>&</sup>lt;sup>1</sup>It is also called a *shared action* or a *shared output*.

**Definition 3.12** A production  $R_n$  has an **output conflict** with a production  $R_m$  iff  $\exists W_k$  such  $S_{C(R_n)}[W_k] \neq S_{C(R_m)}[W_k]$ .

Productions that can fire locally are classified as Independent of Network Transactions (INT) or Dependent on Network Transactions (DNT), according to their dependencies with other productions that belong to other processors. INT and DNT productions have to be processed differently for correct execution according to the serializable criterion. The following definition states that a production that can fire locally is DNT if and only if any of the following conditions hold:

- (i) two of the antecedents of the production are changed by the consequents of a single production allocated to another processor: one of these changes produces an enabling dependency and the other produces a disabling one;

- (ii) the production has two conflicting writes with a production allocated to another processor;

- (iii) the production has an output conflict and a disabling dependency with a production allocated to another processor.

**Definition 3.13** A production  $R_n \in P_i$  is **DNT** iff  $R_n$  can fire locally and any of the following conditions hold:

- (i).  $\exists W_k, W_l$ , and  $R_m \in P_j \neq P_i$  such that  $W_k$  and  $W_l$  are pseudo-local for  $P_i, S_{A(R_n)}[W_k] \neq S_{C(R_m)}[W_k]$ , and  $S_{A(R_n)}[W_l] = S_{C(R_m)}[W_l]$ .

- (ii).  $\exists W_k, W_l$ , and  $R_m \in P_j \neq P_i$  such that  $W_k$  and  $W_l$  are pseudo-local for  $P_i, S_{C(R_n)}[W_k] \neq S_{C(R_m)}[W_k]$ , and  $S_{C(R_n)}[W_l] \neq S_{C(R_m)}[W_l]$ .

(iii).  $\exists W_k, W_l$ , and  $R_m \in P_j \neq P_i$  such that  $W_k$  and  $W_l$  are pseudo-local for  $P_i, S_{A(R_n)}[W_k] \neq S_{C(R_m)}[W_k]$ , and  $S_{C(R_n)}[W_l] \neq S_{C(R_m)}[W_l]$ .

**Definition 3.14** A production  $R_n$  is **INT** iff  $R_n$  can fire locally and  $R_n$  is not **DNT**.

An INT production can start firing at any time as long as its antecedents are satisfied. A DNT production  $P_i$  only starts firing after all tokens generated by a production  $P_j$ , currently being fired by a remote processor, are broadcast in the network and consumed by the processor that fires  $P_i$ . This prevents  $P_i$  and  $P_j$  actions from being intermingled, avoiding thus non-serializable behavior.

## 3.2 System Overview

The parallel architecture presented in this dissertation stems from the realization that improvements restricted to the matching phase of the traditional match-select-act cycle of Production Systems (PS) fail to produce significant speedup. Even machines that allow concurrent execution of the acting and matching phases, while maintaining the global production selection, yield limited improvements in speed. The architecture proposed here allows parallel firing of productions allocated to distinct processors. Within a processor, activities related to matching, acting and selecting are concurrent. Thus the next instantiation to be fired may be selected even before the Rete Network updates due to a previous production firing are completed.

Such aggressive parallelism is possible because the concept of a match-selectact cycle is eliminated. The principle of firing the most recent and specific instantiation is replaced by an approximation of it: only instantiations that are known at the time of the selection are considered, we call this a *partially informed* selection mechanism. The use of associative memories allows for quick elimination of instantiations that are no longer fireable. We also replace the restrictive commutativity criterion by the serializability criterion of correctness. The use of serializability reduces the number of situations in which synchronization is necessary, increasing the amount of parallelism available.

The observation that in production systems reading operations are much more frequent than writing operations motivates an architecture based on a broadcasting network over which only writing operations occur. Such an architectural model imposes limits to the number of processors used. However, two characteristics of PS make them compatible with an architecture with a moderate number of processors: the amount of inter-production parallelism is limited and, as a PS grows, the size of the database grows much faster than its production set.

The parallel architecture is formed by identical processors connected via a Broadcasting Interconnection Network (BIN), as shown on Figure 3.1. At start-up the I/O processor (I/OP) loads the productions on all processors. System level I/O and user interface are also handled through the I/OP. The main components of each processor are the Snooping Directory (SD), the Matching Engine (ME), the Production Controller (PC) and the Instantiation Controller (IC). The Snooping Directory is an associative memory that identifies whether a token broadcast on the BIN conveys an action relevant to the local processor. Relevant tokens are kept in a Broadcasting Network Buffer (BNB) until the IC and the ME are able to process it. The Matching Engine is a Rete-based matcher that implements a state-saving algorithm. The IC uses specialized memory structures to maintain and rapidly update the list of fireable instantiations. To perform this task, it has to monitor the outputs of ME as well as the firing of local (through PC) and global (through SD) productions. One of the memories controlled by IC is the Firing Instantiation Memory (FIM) that keeps a list of all the production instantiations that are enabled to fire. The Production Controller (PC) selects an instantiation to be fired from the list maintained by IC, and, whenever necessary, synchronizes the production firing with BIN operations to guarantee that production firings appear to be atomic.

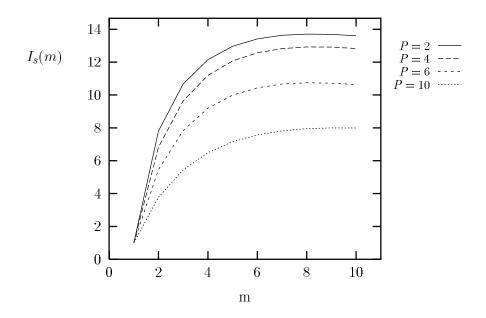

Figure 3.1: Parallel Machine Model