Origin2000<sup>™</sup> and Onyx2<sup>™</sup> Performance Tuning and Optimization Guide

Document Number 007-3430-002

#### CONTRIBUTORS

Written by David Cortesi, based on the first edition by Jeff Fier Illustrated by Dan Young Edited by Christina Cary

Production by Kirsten Pekarek

Engineering contributions by David Cortesi, Leo Dagum, Wesley Jones, Eric Salo, Igor Zacharov, Marco Zagha

St. Peter's Basilica image courtesy of ENEL SpA and InfoByte SpA. Disk Thrower image courtesy of Xavier Berenguer, Animatica.

© 1998, Silicon Graphics, Inc.— All Rights Reserved

The contents of this document may not be copied or duplicated in any form, in whole or in part, without the prior written permission of Silicon Graphics, Inc.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and/or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is Silicon Graphics, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94043-1389.

Silicon Graphics, CHALLENGE, Indy, IRIX, and Onyx are registered trademarks and the Silicon Graphics logo, InfiniteReality, O2, Onyx2, Origin200, Origin2000, POWER CHALLENGE, POWER CHALLENGE 10000, and XFS are trademarks of Silicon Graphics, Inc. CRAY is a registered trademark, and CrayLink is a trademark of Cray Research, Inc. POSIX is a trademark of IEEE. MIPS, R4000, R4400, R5000, R8000, and R10000 are registered trademarks and MIPSpro is a trademark of MIPS Technologies, Inc. NFS is a registered trademark of Sun Microsystems, Inc. X Window System is a trademark of X Consortium, Inc. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, Ltd.

Origin2000<sup>™</sup> and Onyx2<sup>™</sup> Performance Tuning and Optimization Guide Document Number 007-3430-002

# Contents

1.

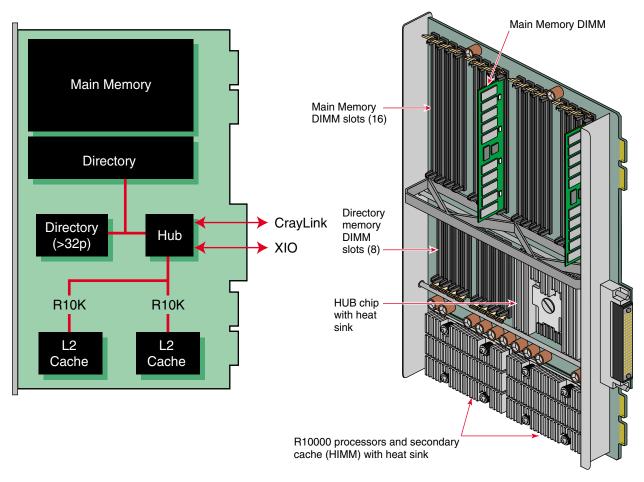

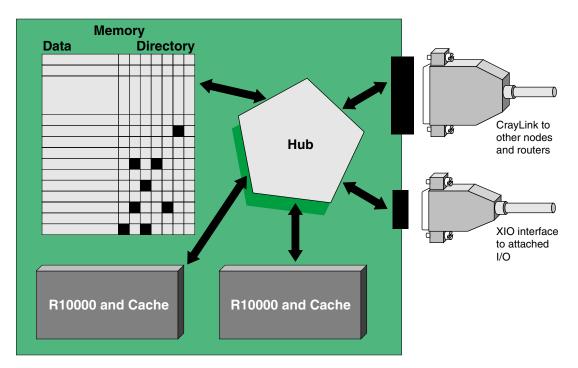

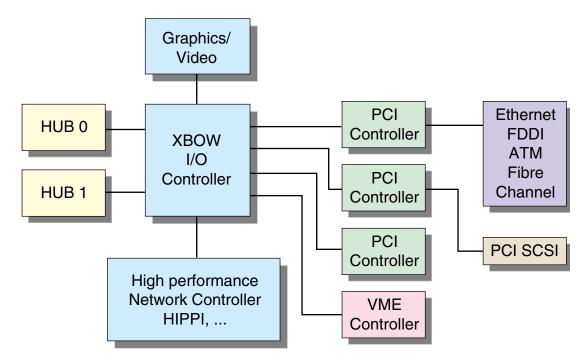

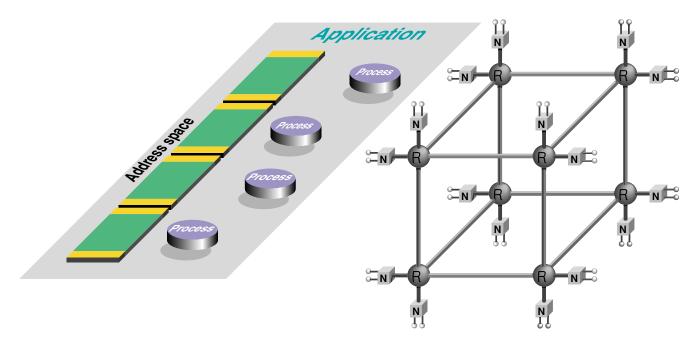

List of Examples xvii List of Figures xxiii List of Tables xxv About This Guide xxvii Who Can Benefit from This Guide xxvii What the Guide Contains xxviii Related Documents xxix Related Manuals xxix Hardware Manuals xxix Compiler Manuals xxix Software Tool Manuals xxx Third-Party Resources xxx Related Reference Pages xxxi Text Conventions xxxii Understanding SN0 Architecture 1 Understanding Scalable Multiprocessor Memory 1 Memory for Multiprocessors 1 Shared Memory Multiprocessing 1 Distributed Memory Multiprocessing 3

Scalability in Multiprocessors 4

Scalability and Shared, Distributed Memory 5

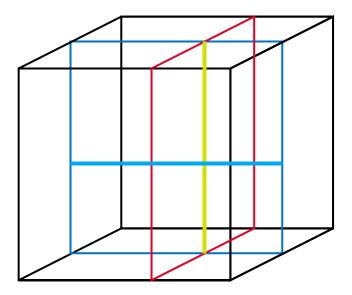

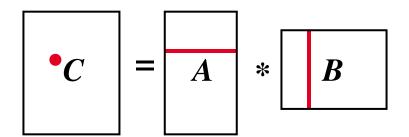

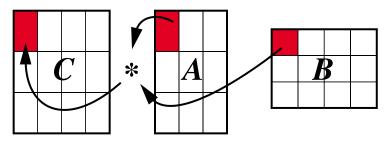

Understanding Scalable Shared Memory 6 SN0 Organization 6 SN0 Memory Distribution 8 SN0 Node Board 10 CPUs and Memory 11 Memory Overhead Bits 11 Hub and CrayLink 11 XIO Connection 12 Understanding Cache Coherency 12 Coherency Methods 13 Understanding Directory-Based Coherency 13 Modifying Shared Data 15 Reading Modified Data 15 Other Protocols 16 Memory Contention 16 SN0 Input/Output 16 I/O Connections and Bandwidth 17 I/O Access to Memory 18 SN0 Latencies and Bandwidths 18 Understanding MIPS R10000 Architecture 20 Superscalar CPU Features 20 MIPS IV Instruction Set Architecture 21 Cache Architecture 22 Level-1 Cache 22 Level-Two Cache 23 Out-of-Order and Speculative Execution 24 Executing Out of Order 24 Queued and Active Instructions 24 Speculative Execution 25 Summary 26

| 2. SN0 Memory Management 27                                    |                                                  |

|----------------------------------------------------------------|--------------------------------------------------|

|                                                                | Dealing With Nonuniform Access Time 27           |

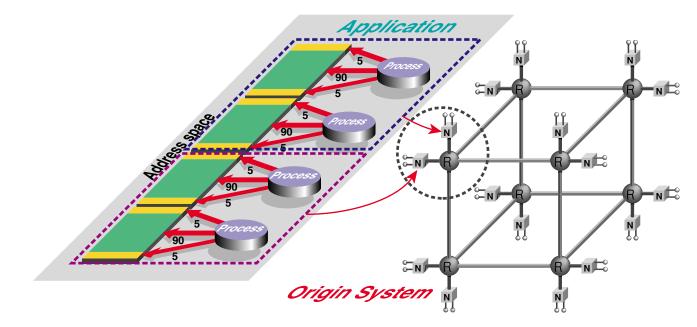

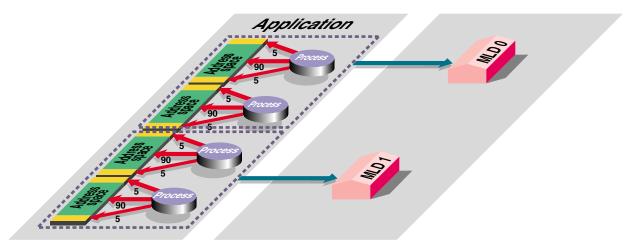

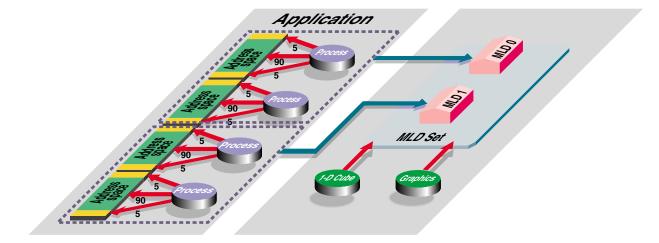

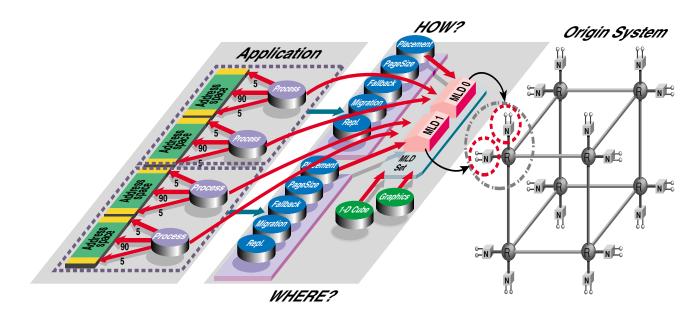

|                                                                | IRIX Memory Locality Management 29               |

|                                                                | Strategies for Memory Locality 29                |

|                                                                | Topology-aware Memory Allocation 29              |

|                                                                | Dynamic Page Migration 30                        |

|                                                                | Replication of Read-Only Pages 30                |

|                                                                | Placing Processes Near Memory 30                 |

|                                                                | Memory Affinity Scheduling 31                    |

| Support for Tuning Options 31<br>Memory Locality Management 31 |                                                  |

|                                                                |                                                  |

| Policy Modules 38                                              |                                                  |

|                                                                | Memory Placement for Single-Threaded Programs 39 |

|                                                                | Data Placement Policies 40                       |

|                                                                | Using First-Touch Placement 40                   |

|                                                                | Using Round-Robin Placement 41                   |

|                                                                | Using Fixed Placement 41                         |

|                                                                | Achieving Good Performance in a NUMA System 42   |

|                                                                | Single-Threaded Programs under NUMA 42           |

|                                                                | Parallel Programs under NUMA 42                  |

| Summary 44                                                     |                                                  |

| 3.                                                             | Tuning for a Single Process 45                   |

|                                                                | Getting the Right Answers 46                     |

|                                                                | Selecting an ABI and ISA 46                      |

|                                                                | Old 32-Bit ABI 46                                |

|                                                                | New 32-Bit ABI 47                                |

|                                                                | 64-Bit ABI 47                                    |

|                                                                | Specifying the ABI 47                            |

|                                                                | Dealing with Porting Issues 48                   |

|                                                                | Uninitialized Variables 48                       |

|                                                                | Computational Differences 48                     |

#### Contents

|    | Exploiting Existing Tuned Code 49              |

|----|------------------------------------------------|

|    | Standard Math Library 49                       |

|    | libfastm Library 50                            |

|    | CHALLENGEcomplib Library 50                    |

|    | SCSL Library 51                                |

|    | Summary 51                                     |

| 4. | Profiling and Analyzing Program Behavior 53    |

|    | Profiling Tools 53                             |

|    | Analyzing Performance with Perfex 54           |

|    | Taking Absolute Counts of One or Two Events 54 |

|    | Taking Statistical Counts of All Events 55     |

|    | Getting Analytic Output with the -y Option 56  |

|    | Interpreting Maximum and Typical Estimates 58  |

|    | Interpreting Statistical Metrics 59            |

|    | Processing perfex Output 61                    |

|    | Collecting Data over Part of a Run 61          |

|    | Using perfex with MPI 62                       |

|    | Using SpeedShop 62                             |

|    | Taking Sampled Profiles 63                     |

|    | Understanding Sample Time Bases 63             |

|    | Sampling through Hardware Event Counters 65    |

|    | Performing ssrun Experiments 65                |

|    | Sampling Through Other Hardware Counters 66    |

|    | Displaying Profile Reports from Sampling 67    |

|    | Using Ideal Time Profiling 68                  |

|    | Capturing an Ideal Time Trace 69               |

|    | Default Ideal Time Profile 69                  |

|    | Interpreting the Ideal Time Report 71          |

|    | Removing Clutter from the Report 72            |

|    | Including Line-Level Detail 73                 |

|    | Creating a Compiler Feedback File 75           |

|    | Displaying Operation Counts 75                 |

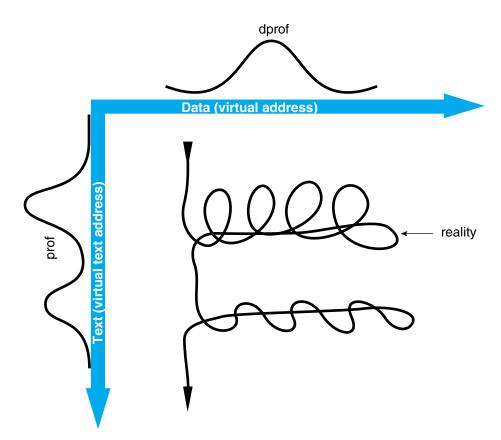

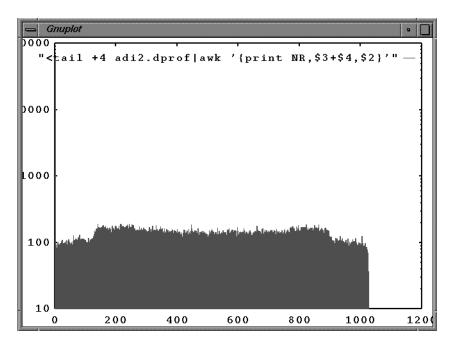

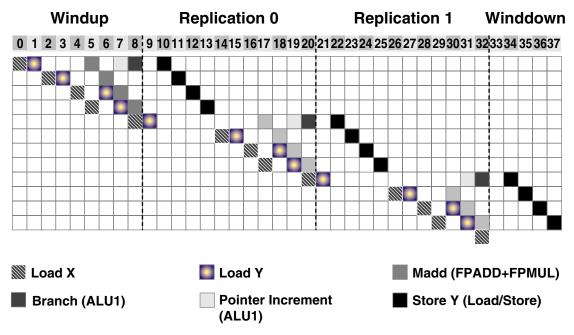

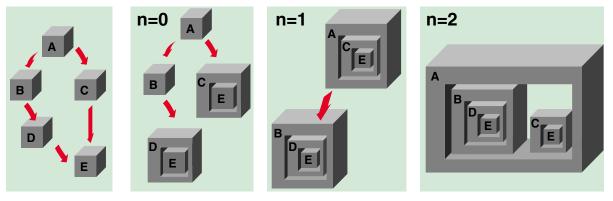

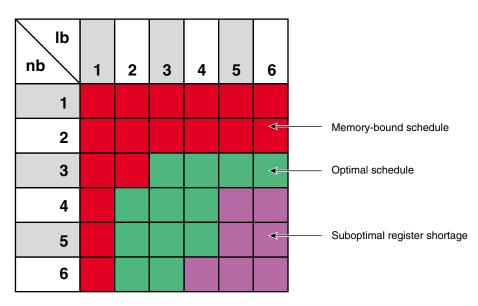

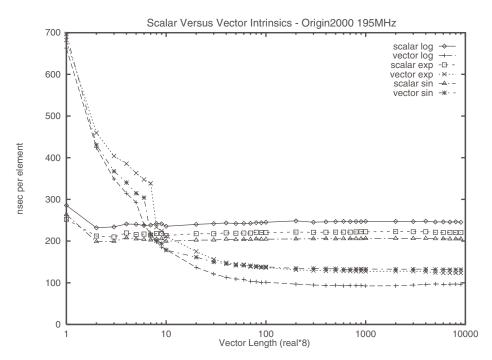

Profiling the Call Hierarchy 76 Displaying Ideal Time Call Hierarchy 77 Displaying Usertime Call Hierarchy 79 Using Exception Profiling 81 Profiling Exception Frequency 81 Understanding Treatment of Underflow Exceptions 81 Using Address Space Profiling 82 Applying dprof 84 Interpreting dprof Output 85 Applying dlook 86 Summary 87 **Using Basic Compiler Optimizations** 89 Understanding Compiler Options 90 Recommended Starting Options 90 Compiler Option Groups 91 Compiler Defaults 92 Using a Makefile 92 Setting Optimization Level with -On 93 Start with -O2 for All Modules 93 Compile -O3 or -Ofast for Critical Modules 94 Use -O0 for Debugging 94 Setting Target System with -TARG 95 Understanding Arithmetic Standards 95 IEEE Conformance 96 Roundoff Control 97 Exploiting Software Pipelining 99 Understanding Software Pipelining 99 Pipelining the DAXPY Loop 101 Reading Software Pipelining Messages 105 Enabling Software Pipelining with -O3 108 Dealing with Software Pipelining Failures 108

5.

Informing the Compiler 109 Understanding Aliasing Models 109 Use Alias=Restrict When Possible 110 Use Alias=Disjoint When Necessary 112 Breaking Other Dependencies 115 Improving C Loops 118 Permitting Speculative Execution 121 Software Speculative Execution 121 Hardware Speculative Execution 122 Controlling the Level of Speculation 123 Passing a Feedback File 124 Exploiting Interprocedural Analysis 125 Requesting IPA 126 Compiling and Linking with IPA 126 Compile Time with IPA 127 Understanding Inlining 128 Using Manual Inlining 129 Using Automatic Inlining 132 IPA Programming Hints 134 Summary 134 6. **Optimizing Cache Utilization** 135 Understanding the Levels of the Memory Hierarchy 135 Understanding Level-One and Level-Two Cache Use 135 Understanding TLB and Virtual Memory Use 136 Degrees of Latency 137 Understanding Prefetching 137 Principles of Good Cache Use 138 Using Stride-One Access 138 Grouping Data Used at the Same Time 139 Understanding Cache Thrashing 140 Using Array Padding to Prevent Thrashing 142

Identifying Cache Problems with Perfex and SpeedShop 142 Diagnosing and Eliminating Cache Thrashing 144 Diagnosing and Eliminating TLB Thrashing 145 Using Copying to Circumvent TLB Thrashing 146 Using Larger Page Sizes to Reduce TLB Misses 147 Using Other Cache Techniques 148 Understanding Loop Fusion 148 Understanding Cache Blocking 149 Understanding Transpositions 153 Summary 156 7. Using Loop Nest Optimization 157 Understanding Loop Nest Optimizations 157 Requesting LNO 158 Reading the Transformation File 158 Using Outer Loop Unrolling 159 Controlling Loop Unrolling 164 Using Loop Interchange 165 Combining Loop Interchange and Loop Unrolling 166 Controlling Cache Blocking 167 Adjusting Cache Blocking Block Sizes 168 Adjusting the Optimizer's Cache Model 170 Using Loop Fusion and Fission 170 Using Loop Fusion 170 Using Loop Fission 171 Controlling Fission and Fusion 173 Using Prefetching 174 Prefetch Overhead and Unrolling 175 Using Pseudo-Prefetching 176 Controlling Prefetching 177 Using Manual Prefetching 178

#### Contents

8.

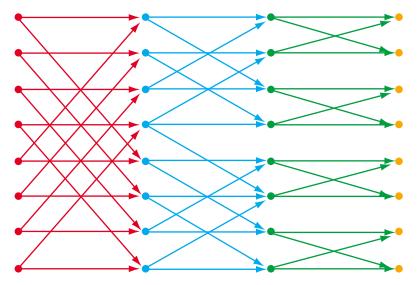

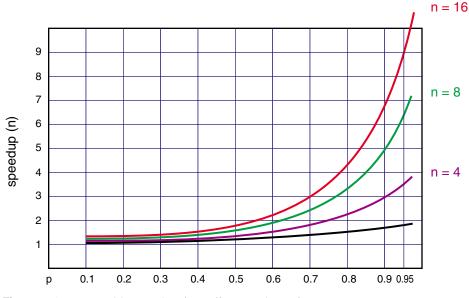

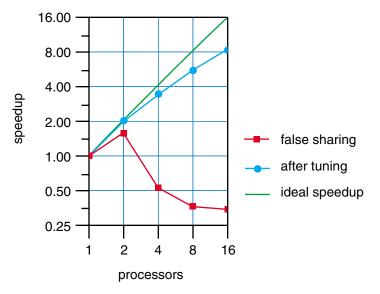

Using Array Padding 180 Using Gather-Scatter and Vector Intrinsics 182 Understanding Gather-Scatter 182 Vector Intrinsics 183 Summary 185 Tuning for Parallel Processing 187 Understanding Parallel Speedup and Amdahl's Law 188 Adding CPUs to Shorten Execution Time 188 Understanding Parallel Speedup 189 Understanding Superlinear Speedup 190 Understanding Amdahl's Law 190 Calculating the Parallel Fraction of a Program 191 Predicting Execution Time with n CPUs 192 Compiling Serial Code for Parallel Execution 193 Compiling a Parallel Version of a Program 193 Controlling a Parallelized Program at Run Time 193 Explicit Models of Parallel Computation 194 Fortran Source with Directives 194 C and C++ Source with Pragmas 195 Message-Passing Models MPI and PVM 195 C Source Using POSIX Threads 196 C and C++ Source Using UNIX Processes 196 Tuning Parallel Code for SN0 196 Prescription for Performance 197 Ensuring That the Program Is Properly Parallelized 197 Finding and Removing Memory Access Problems 198 Diagnosing Cache Problems 199 Identifying False Sharing 200 Correcting Cache Contention in General 203

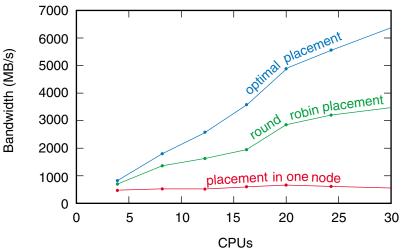

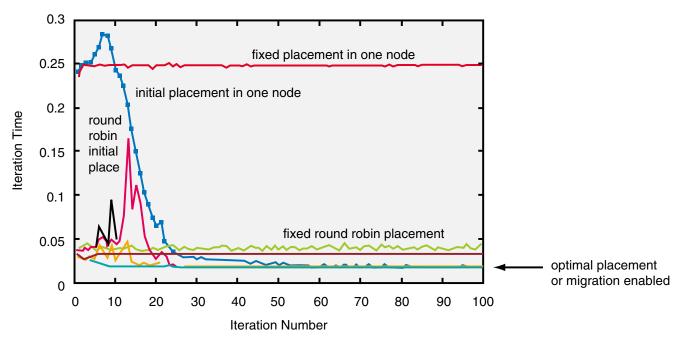

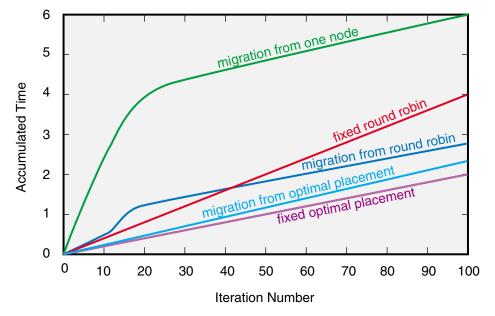

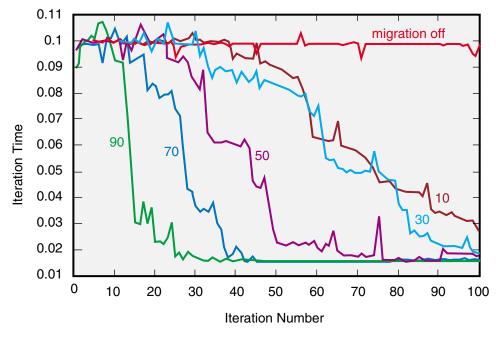

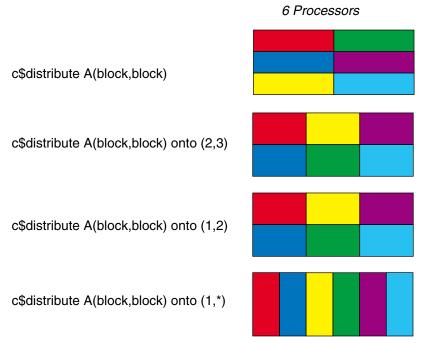

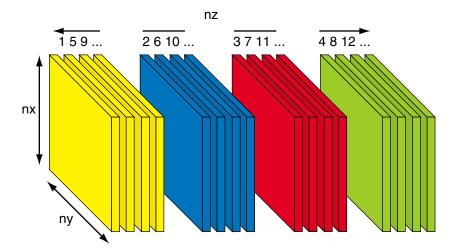

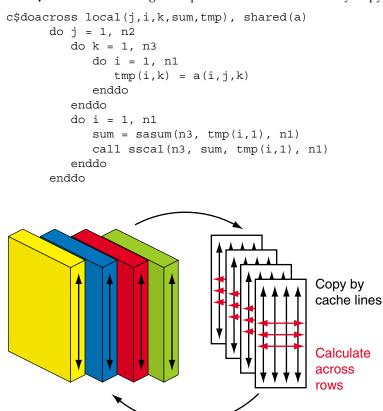

Scalability and Data Placement 205 Tuning Data Placement for MP Library Programs 206 Trying Round-Robin Placement 207 Trying Dynamic Page Migration 209 Combining Migration and Round-Robin Placement 210 Experimenting with Migration Levels 213 Tuning Data Placement without Code Modification 215 Modifying the Code to Tune Data Placement 215 Programming For First-Touch Placement 216 First-Touch Placement with Multiple Data Distributions 219 Using Data Distribution Directives 222 Understanding Directive Syntax 222 Using Distribute for Loop Parallelization 223 Using the Distribute Directive 224 Using Parallel Do with Distributed Data 224 Understanding Distribution Mapping Options 225 Understanding the ONTO Clause 227 Understanding the AFFINITY Clause for Data 228 Understanding the AFFINITY Clause for Threads 228 Understanding the NEST Clause 229 Understanding the Redistribution Directives 230 Using the Page\_Place Directive for Custom Mappings 231 Using Reshaped Distribution Directives 232 Creating Your Own Reshaped Distribution 237 Restrictions of Reshaped Distribution 237 Investigating Data Distributions 239 Using \_DSM\_VERBOSE 239 Using Dynamic Placement Information 240

A.

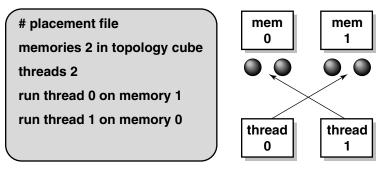

Non-MP Library Programs and Dplace 243 Changing the Page Size 244 Enabling Page Migration 245 Specifying the Topology 246 Placement File Syntax 248 Using Environment Variables in Placement Files 248 Using the memories Statement 249 Using the threads Statement 249 Assigning Threads to Memories 250 Indicating Resource Affinity 251 Assigning Memory Ranges 252 Using the dplace Library for Dynamic Placement 252 Using dplace with MPI 3.1 254 Advanced Options 255 Summary 256 Bentley's Rules Updated 257 Space-for-Time Rules 257 Data Structure Augmentation 257 Store Precomputed Results 258 Caching 258 Lazy Evaluation 259 Time-for-Space Rules 259 Packing 259 Interpreters 260 Loop Rules 260 Code Motion Out of Loops 260 Combining Tests 261 Loop Unrolling 261 Transfer-Driven Loop Unrolling 262 Unconditional Branch Removal 262 Loop Fusion 263

Logic Rules 264 Exploit Algebraic Identities 264 Short-Circuit Monotone Functions 264 Reorder Tests 265 Precompute Logical Functions 266 Replace Control Variables with Control Statements 266 Procedure Design Rules 267 Collapse Procedure Hierarchies 267 Exploit Common Cases 267 Use Coroutines 268 Transform Recursive Procedures 268 Use Parallelism 269 Expression Rules 269 Initialize Data Before Runtime 269 Initializing to Zero 270 Initializing from Files 270 Exploit Algebraic Identities 271 Eliminate Common Subexpressions 272 Combine Paired Computation 272 Exploit Word Parallelism 272 R10000 Counter Event Types 273 Counter Events In Detail 275 Clock Cycles 275 Instructions Issued and Done 275 Issued Instructions (Event 1) 275 Issued Loads (Event 2) 276 Issued Stores (Event 3) 276 Instructions Done (Event 14) 276

B.

| Graduated Instructions 277                                                |

|---------------------------------------------------------------------------|

| Issued Versus Graduate Loads and Stores 277                               |

| Graduated Instructions (Event 15) 278                                     |

| Graduated Instructions (Event 17) 278                                     |

| Graduated Loads (Event 18) 278                                            |

| Graduated Stores (Event 19) 278                                           |

| Graduated Floating Point Instructions (Event 21) 278                      |

| Branching Instructions 278                                                |

| Decoded Branches (Event 6) 279                                            |

| Mispredicted Branches (Event 24) 279                                      |

| Primary Cache Use 279                                                     |

| Primary Instruction Cache Misses (Event 9) 280                            |

| Primary Data Cache Misses (Event 25) 280                                  |

| Quadwords Written Back from Primary Data Cache (Event 22) 280             |

| Secondary Cache Use 280                                                   |

| Quadwords Written Back from Scache (Event 7) 280                          |

| Correctable Scache Data Array ECC Errors (Event 8) 281                    |

| Secondary Instruction Cache Misses (Event 10) 281                         |

| Instruction Misprediction from Scache Way Prediction Table (Event 11) 281 |

| Secondary Data Cache Misses (Event 26) 281                                |

| Data Misprediction from Scache Way Prediction Table (Event 27) 281        |

| Store or Prefetch-Exclusive to Clean Block in Scache (Event 30) 282       |

| Store or Prefetch-Exclusive to Shared Block in Scache (Event 31) 282      |

| Cache Coherency Events 282                                                |

| External Interventions (Event 12) 283                                     |

| External Invalidations (Event 13) 283                                     |

| Virtual Coherency Conditions (Old Event 14) 283                           |

| External Intervention Hits in Scache (Event 28) 283                       |

| External Invalidation hits in Scache (Event 29) 283                       |

| Virtual Memory Use 284                                                    |

| TLB Misses (Event 23) 284                                                 |

Contents

| Lock-Handling Instructions 284            |  |  |

|-------------------------------------------|--|--|

| Issued Store Conditionals (Event 4) 284   |  |  |

| Failed Store Conditionals (Event 5) 285   |  |  |

| 20 Graduated store conditionals 285       |  |  |

| C. Useful Scripts and Code 287            |  |  |

| Program adi2 288                          |  |  |

| Basic Makefile 292                        |  |  |

| Software Pipeline Script swplist 294      |  |  |

| Shell Script ssruno 297                   |  |  |

| Awk Script for Perfex Output 298          |  |  |

| Awk Script for Amdahl's Law Estimation 30 |  |  |

| Page Address Routine va2pa() 302          |  |  |

| CPU Clock Rate Routine cpuclock() 303     |  |  |

| Glossary 305                              |  |  |

Index 317

xv

# List of Examples

| Example 1-1                                     | le 1-1 Parallel Code Using Directives for Simple Scheduling 2         |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------|--|--|

| Example 1-2                                     | Example 1-2 Parallel Code Using Directives for Interleaved Scheduling |  |  |

| Example 4-1                                     | Example 4-1 Experimenting with perfex 54                              |  |  |

| Example 4-2                                     |                                                                       |  |  |

| Example 4-3                                     | Output of perfex -a -y 56                                             |  |  |

| Example 4-4                                     | Performing an ssrun Experiment 66                                     |  |  |

| Example 4-5                                     | Example Run of ssruno 66                                              |  |  |

| Example 4-6                                     | ample 4-6 Default prof Report from ssrun Experiment 67                |  |  |

| Example 4-7                                     | xample 4-7Profile at the Source Line Level Using prof -heavy68        |  |  |

| Example 4-8                                     | nple 4-8 Ideal Time Profile Run 69                                    |  |  |

| Example 4-9                                     | -9 Default Report of Ideal Time Profile 69                            |  |  |

| Example 4-10                                    | Ideal Time Report Truncated with -quit 72                             |  |  |

| Example 4-11                                    | 1 Ideal Time Report by Lines 73                                       |  |  |

| Example 4-12                                    | Ideal Time Profile Using -lines and -only Options 74                  |  |  |

| Example 4-13                                    | Ideal Time Architecture Information Report 75                         |  |  |

| Example 4-14                                    | -14 Extract from a Butterfly Report 77                                |  |  |

| Example 4-15                                    | xample 4-15 Usertime Call Hierarchy 79                                |  |  |

| Example 4-16 Application of dprof 84            |                                                                       |  |  |

| Example 4-17 Example of Default dlook Output 87 |                                                                       |  |  |

| Example 5-1                                     | Simple Summation Loop 97                                              |  |  |

| Example 5-2                                     | Unrolled Summation Loop 98                                            |  |  |

| Example 5-3                                     | Example 5-3 Basic DAXPY Loop 99                                       |  |  |

| Example 5-4                                     | Example 5-4 Unrolled DAXPY Loop 102                                   |  |  |

| Example 5-5                                     | Compiler-Generated DAXPY Schedule 103                                 |  |  |

| Example 5-6                                     | Basic DAXPY Loop Code 105                                             |  |  |

| Example 5-7                                     | Sample Software Pipeline Report Card 106                              |  |  |

| Example 5-8                                     | cample 5-8 C Implementation of DAXPY Loop 111                         |  |  |

Example 5-9 SWP Report Card for C Loop with Default Alias Model 111 Example 5-10 SWP Report Card for C Loop with Alias=Restrict 112 Example 5-11 C Loop Nest on Multidimensional Array 112 Example 5-12 SWP Report Card for Stencil Loop with Alias=Restrict 114 Example 5-13 SWP Report Card for Stencil Loop with Alias=Disjoint 114 Example 5-14 Indirect DAXPY Loop 115 Example 5-15 SWP Report Card on Indirect DAXPY 115 Example 5-16 Indirect DAXPY in Fortran with ivdep 116 Example 5-17 Indirect DAXPY in C with ivdep 116 SWP Report Card for Indirect DAXPY with ivdep 116 Example 5-18 Example 5-19 Loop with Two Types of Dependency 117 Example 5-20 C Loop with Obvious Loop-Carried Dependence 117 Example 5-21 C Loop with Lexically-Forward Dependency 118 Example 5-22 C Loop Test Using Dereferenced Pointer 118 Example 5-23 C Loop Test Using Local Copy of Dereferenced Pointer 119 Example 5-24 C Loop with Disguised Invariants 119 Example 5-25 SWP Report Card for Loop with Disguised Invariance 120 Example 5-26 C Loop with Invariants Exposed 120 Example 5-27 SWP Report Card for Modified Loop 121 Example 5-28 Conventional Code to Avoid an Exception 122 Example 5-29 Speculative Equivalent Permitting an Exception 122 Example 5-30 Code Suitable for Inlining 129 Example 5-31 Subroutine Candidates for Inlining 130 Example 5-32 Inlined Code from w2f File 131 Example 6-1 Simple Loop Nest with Poor Cache Use 138 Example 6-2 Reversing Loop Nest to Achieve Stride-One Access 139 Example 6-3 Loop Using Three Vectors 139 Example 6-4 Three Vectors Combined in an Array 140 Fortran Code Likely to Cause Thrashing 140 Example 6-5 Example 6-6 Perfex Data for adi2.f 144 Example 6-7 Perfex Data for adi5.f 145 Perfex Data for adi53.f 147 Example 6-8

| Example 6-9                                                              | Sequence of DAXPY and Dot-Product on a Single Vector 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Example 6-10                                                             | DAXPY and Dot-Product Loops Fused 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Example 6-11                                                             | Matrix Multiplication Loop 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Example 7-1                                                              | Matrix Multiplication Subroutine 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| <b>Example 7-2</b> SWP Report Card for Matrix Multiplication 160         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Example 7-3                                                              | Matrix Multiplication Unrolled on Outer Loop 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Example 7-4                                                              | Matrix Multiplication Unrolled on Middle Loop 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Example 7-5                                                              | Matrix Multiplication Unrolled on Outer and Middle Loops 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Example 7-6                                                              | Simple Loop Nest with Poor Cache Use 165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| <b>Example 7-7</b> Simple Loop Nest Interchanged for Stride-1 Access 165 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| <b>Example 7-8</b> Loop Nest with Data Recursion 165                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Example 7-9                                                              | Recursive Loop Nest Interchanged and Unrolled 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Example 7-10                                                             | Matrix Multiplication in C 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Example 7-11                                                             | Cache-Blocked Matrix Multiplication 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Example 7-12                                                             | Performance Provide America |  |

| Example 7-13                                                             | <b>Example 7-13</b> Fortran Loop with Explicit Cache Block Sizes and Interchange 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Example 7-14                                                             | Example 7-14 Transformed Fortran Loop 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Example 7-15                                                             | <b>Example 7-15</b> Adjacent Loops that Cannot be Fused 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Example 7-16                                                             | Adjacent Loops Fused After Peeling 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| <b>Example 7-17</b> Sketch of a Loop with a Long Body 171                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| <b>Example 7-18</b> Sketch of a Loop After Fission 172                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Example 7-19                                                             | Loop Nest that Cannot Be Interchanged 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Example 7-20                                                             | Loop Nest After Fission and Interchange 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Example 7-21                                                             | <b>Example 7-21</b> Simple Reduction Loop Needing Prefetch 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Example 7-22                                                             | <b>Example 7-22</b> Simple Reduction Loop with Prefetch 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |